# MAPPING AND FPGA GLOBAL ROUTING USING MEAN FIELD ANNEALING

#### A THESIS

SUBMITTED TO THE DEPARTMENT OF COMPUTER

ENGINEERING AND INFORMATION SCIENCE

AND THE INSTITUTE OF ENGINEERING AND SCIENCE

OF BİLKENT UNIVERSITY

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

MASTER OF SCIENCE

By İsmail Haritaoğlu September, 1994

| in scope and in quality, as a thesis for t                                            |                                     |

|---------------------------------------------------------------------------------------|-------------------------------------|

| Asst. Prof. (                                                                         | Cevdet Aykanat (Advisor)            |

| I certify that I have read this thesis and in scope and in quality, as a thesis for t |                                     |

| Assoc                                                                                 | . Prof. Ömer Benli                  |

| I certify that I have read this thesis and in scope and in quality, as a thesis for t |                                     |

| Asst. I                                                                               | Prof. Mustafa Pinar                 |

| Approved for the Institute of                                                         | Engineering and Science:            |

| Prof                                                                                  | . Mehmet Baray cor of the Institute |

#### ABSTRACT

# MAPPING AND FPGA GLOBAL ROUTING USING MEAN FIELD ANNEALING

İsmail Haritaoğlu M.S. in Computer Engineering and Information Science Advisor: Asst. Prof. Cevdet Aykanat September, 1994

Mean Field Annealing algorithm which was proposed for solving combinatorial optimization problems combines the properties of neural networks and Simulated Annealing. In this thesis, MFA is formulated for mapping problem in parallel processing and global routing problem in physical design automation of Field Programmable Gate Array (FPGAs) A new Mean Field Annealing (MFA) formulation is proposed for the mapping problem for mesh-connected and hypercube architectures. The proposed MFA heuristic exploits the conventional routing scheme used in mesh and hypercube interconnection topologies to introduce an efficient encoding scheme. An efficient implementation scheme which decreases the complexity of the proposed algorithm by asymptotical factors is also developed. Experimental results also show that the proposed MFA heuristic approaches the speed performance of the fast Kernighan-Lin heuristic while approaching the solution quality of the powerful simulated annealing heuristic. Also, we propose an order-independent global routing algorithm for SRAM type FPGAs based on Mean Field Annealing. The performance of the proposed global routing algorithm is evaluated in comparison with LocusRoute global router on ACM/SIGDA Design Automation benchmarks. Experimental results indicate that the proposed MFA heuristic performs better than the LocusRoute.

$Keywords\colon \textsc{Mapping},$ Global Routing, Field Programmable Gate Arrays, Mean Field Annealing

#### ÖZET

#### ORTA ALAN TAVLAMA METODU KULLANILARAK EŞLEME VE FPGA'LERDEKİ KABA ROTALAMA PROBLEMLERİNİN ÇÖZÜMÜ

İsmail Haritaoğlu Bilgisayar ve Enformatik Mühendisliği, Yüksek Lisans Danışman: Yrd. Doç. Dr. Cevdet Aykanat Eylül, 1994

Birleşimsel eniyileme problemlerini çözmek için önerilen Ortak Alan Tavlama (Mean Field Annealing) algoritması, sinir ağları ve benzetimsel tavlama (Simulated Annealing) yöntemlerinin özelliklerini taşır. Bu çalışmada, Ortak Alan Tavlama algoritması Alan Programlamalı Kapı Devrelerinin (Field Programmable Gate Arrays) kaba rotalama problemine (Global Routing) ve paralel programlamadakı eşleme (Mapping) problemlerine uyarlanmıştır. Tezin ilk bolümünde Ortak Alan Tavlama algoritması Alan Programlamalı Kapı Devrelerinin (Field Programmable Gate Arrays) kaba rotalama problemininin çözümünde kullanılmıştır. Onerilen algoritmalarının başarımları Locus-Route kaba rotalama algoritması ile kıyaslanarak değerlendirilmiştir. Deneyler algoritmaları karşılaştırmak için kullanılan standart devreler (Benchmarks) üzerinde yapılmıştır. Elde edilen sonuçlar Ortak Alan Tavlama algoritmasının kaba rotalama problemini çözmek için iyi bir alternatif algoritma olarak kullanılabileceğini göstermektedir. Tezin ikinci bölümünde Mesh ve Hiperküp tipindeki paralel bilgisayarlarındaki eşleme problemi için daha önce onerilen algoritmalardan daha hızlı olan bir algoritma geliştirilmiş ve bu önerilen algoritmanın başarımları Kernighan-Lin, Simulated Annealing ve daha önce önerilen ortak alan tavlama metotları ile kıyaslanarak değerlendirilmiştir.

Anahtar Sözcükler: Orta Alan tavlama algoritması, Eşleme problemi, Kaba rotalama algoritmaları, Alan programlamlı kapı devreleri

#### ACKNOWLEDGEMENTS

I would like to express my deep gratitude to my supervisor Dr. Cevdet Aykanat for his guidance, suggestions, and invaluable encouragement throughout the development of this thesis. I would like to thank Dr. Ömer Benli for reading and commenting on the thesis. I would also like to thank Dr. — — for reading and commenting on the thesis. I owe special thanks to Dr. Mehmet Baray for providing a pleasant environment for study. I am grateful to my family and my friends for their infinite moral support and help.

Bu çalışmamı, herşeyimi borçlu olduğum  $anneme,\ babama,$  ve Esin'e

adıyorum.

#### Contents

| 1 | INT | RODU    | JCTION                                        | 1  |

|---|-----|---------|-----------------------------------------------|----|

| 2 | ME  | AN FI   | ELD ANNEALING                                 | 4  |

|   | 2.1 | Mean 1  | Field Annealing                               | 4  |

|   |     | 2.1.1   | Ising Model                                   | 5  |

|   |     | 2.1.2   | Potts Model                                   | 6  |

|   |     | 2.1.3   | MFA Algorithm                                 | 8  |

| 3 | FPC | GAs &   | GLOBAL ROUTING                                | 9  |

|   | 3.1 | Introdu | action to Field Programmable Gate Arrays      | 9  |

|   |     | 3.1.1   | Logic Blocks                                  | 10 |

|   |     | 3.1.2   | Programming Technologies                      | 10 |

|   |     | 3.1.3   | Routing Architectures                         | 11 |

|   | 3.2 | Physic  | al Design Automation of FPGAs                 | 15 |

|   |     | 3.2.1   | Partitioning                                  | 15 |

|   |     | 3.2.2   | Placement                                     | 15 |

|   |     | 3.2.3   | Routing                                       | 15 |

|   | 3.3 | Global  | Routing Problem in Design Automation of FPGAs | 16 |

| CONTENTS | viii |

|----------|------|

|----------|------|

|   | 3.4 | Model of FPGA for Global Routing                              | 17         |

|---|-----|---------------------------------------------------------------|------------|

| 4 | MF  | A SOLUTION FOR GLOBAL ROUTING IN FPGA                         | 22         |

|   | 4.1 | MFA Formulation of Global Routing                             | 22         |

|   | 4.2 | Implementation                                                | 25         |

|   | 4.3 | Experimental Results                                          | 27         |

| 5 | TH  | E MAPPING PROBLEM                                             | 33         |

|   | 5.1 | The Mapping Problem                                           | 33         |

|   | 5.2 | The Model of Mapping Problem                                  | 35         |

| 6 | MF  | A SOLUTION FOR MAPPING                                        | <b>3</b> 9 |

|   | 6.1 | General MFA Formulation for Mapping Problem                   | 39         |

|   | 6.2 | Interconnection-Topology Specific MFA Formulation for Mapping | 42         |

|   |     | 6.2.1 MFA formulation for Mesh-Connected Architectures        | 42         |

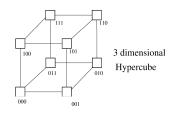

|   |     | 6.2.2 MFA Formulation For Hypercube Architecture              | 51         |

|   | 6.3 | Performance Evaluation                                        | 56         |

|   | 6.4 | Experimental Results                                          | 59         |

| 7 | CO  | NCLUSION                                                      | 69         |

### List of Figures

| 2.1 | Mean Field Annealing Algorithm                                                                                        | 8  |

|-----|-----------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | The Architecture of General FPGA                                                                                      | 11 |

| 3.2 | Example of flexibilities of FPGA (a) flexibility of switch block (b) flexibility of connection block                  | 12 |

| 3.3 | The Architecture of Xilinx 3000 FPGA                                                                                  | 13 |

| 3.4 | The Architecture of Actel FPGA                                                                                        | 14 |

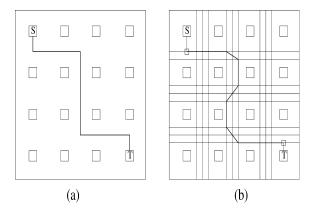

| 3.5 | General approach to FPGA routing a) Global routing b) Detailed routing                                                | 16 |

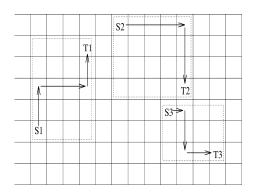

| 3.6 | Sample two bends routes                                                                                               | 17 |

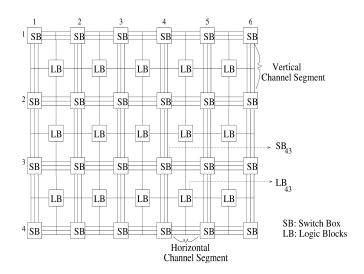

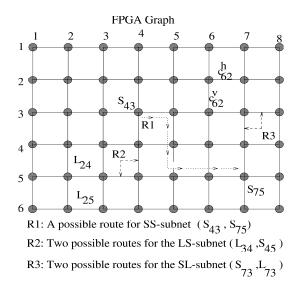

| 3.7 | The FPGA model used for Global Routing                                                                                | 18 |

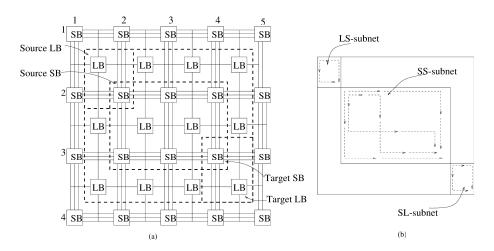

| 3.8 | (a) The routing area of the two-pin net and its subnets, (b) The possible routes for each subnets                     | 19 |

| 3.9 | The Cost Graph for FPGA model                                                                                         | 20 |

| 4.1 | Channel density distribution obtained by MFA for the circuit C1355                                                    | 32 |

| 4.2 | Channel density distribution obtained by LocusRoute for the circuit C1355                                             | 32 |

| 4.3 | SEGA detailed router results of the circuit C1355 for the global routing solutions obtained by (a) MFA (b) LocusRoute | 32 |

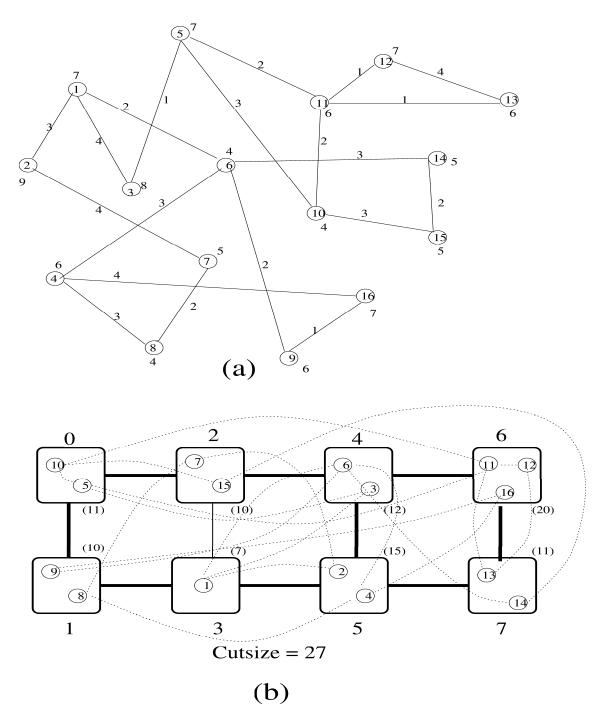

| 5.1 | An example of mapping problem                                                                 | 38 |

|-----|-----------------------------------------------------------------------------------------------|----|

| 6.1 | The proposed efficient MFA algorithm for the mapping problem for mesh-connected Architectures | 48 |

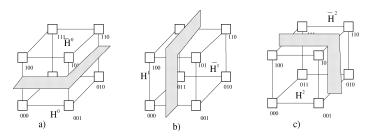

| 6.2 | Three different ways for dividing 3-dimensional hypercube to 2 2-dimensional subcubes         | 52 |

| 6.3 | The Mean field value calculation of given spin i of subcube $H^m$ .                           | 56 |

#### List of Tables

| 4.1 | MCNC benchmark circuits used in experiments                                                                                                                                                                             | 27 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.2 | The Global Router results                                                                                                                                                                                               | 28 |

| 4.3 | The SEGA detailed routing results in area optimization mode .                                                                                                                                                           | 29 |

| 4.4 | The SEGA detailed routing results in speed optimization mode .                                                                                                                                                          | 30 |

| 4.5 | Minimun Channel Width for 100% routing                                                                                                                                                                                  | 31 |

| 6.1 | Total communication costs averages normalized with respect to mesh-specific MFA of the solution found by SA,KL,general MFA and mesh-specific MFA for randomly generated mapping problem instances for various mesh size | 59 |

| 6.2 | Percent computational load imbalance averages of the solution found by SA,KL,general MFA and mesh-specific MFA for randomly generated mapping problem instances for various mesh size                                   | 60 |

| 6.3 | Execution time averages of the solution found by SA,KL,general MFA and mesh-specific MFA for randomly generated mapping problem instances for various mesh size                                                         | 60 |

| 6.4 | Average performance measures of the solution found by SA, KL, general MFA and mesh-specific MFA for randomly generated mapping problem instances                                                                        | 61 |

| 6.5 | The Benchmark Sparce Matrix data used in experiments                                                                                                                                                                    | 62 |

LIST OF TABLES xii

| 6.6  | Total communatication cost averages, normalized with respect to mesh-specific MFA, of the solution found by SA,KL, general MFA and mesh-specific MFA for some bechmark mapping problem instances for various mesh size                 | 63 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 6.7  | Load Imbalanced averages, of the solution found by SA, KL, general MFA and mesh-specific MFA for some bechmark mapping problem instances for various mesh size                                                                         | 64 |

| 6.8  | Total execution time, normalized with respect to mesh-specific MFA, of the solution found by SA,KL, general MFA and mesh-specific MFA for some bechmark mapping problem instances for various mesh size                                | 65 |

| 6.9  | Average performance measures of the solutions found by SA, KL, general MFA and mesh-specific MFA for mapping problem instances                                                                                                         | 66 |

| 6.10 | Total communication costs averages normalized with respect to hypercube-specific MFA of the solution found by SA,KL,general MFA and hypercube-specific MFA for randomly generated mapping problem instances for various hypercube size | 66 |

| 6.11 | Percent computational load imbalance averages of the solution found by SA,KL,general MFA and hypecube-specific MFA for randomly generated mapping problem instances for various hypercube size                                         | 67 |

| 6.12 | Execution time averages of the solution found by SA,KL,general MFA and hypercube-specific MFA for randomly generated mapping problem instances for various hypercubesize                                                               | 67 |

#### Chapter 1

#### INTRODUCTION

A common property of both domain mapping problem in parallel processing and global routing in VLSI is that both problems are combinatorial optimization problems. As many problems in VLSI, parallel processing and other areas, these algorithms involve a finite set of configuration from solutions satisfying a number of rigid requirement are selected. The objective of combinatorial optimization algorithm is to find a solution of the optimum cost provided that a cost can be assigned to each solution. Many combinatorial optimizations problems are hard in the sense that they are NP-hard problems. There are no known deterministic polynomial time algorithms to find the optimal solution to any of those hard problems. The algorithms using the complete enumeration techniques are usually exponential in the size of problem, therefore they require a great amount of time to find the optimal solution. As a result, heuristics that run in a low order polynomial time have been employed to obtain good solutions to these hard problems. Disadvantage of heuristics is that they may get stuck in local minima.

A powerful method for solving combinatorial optimization problem used in previous research is called *Simulated Annealing*. This method is the application of a successful statistical method, which is used to estimate the results of annealing process in statistical mechanics, to combinatorial optimization problems. Simulated Annealing is a general method that guarantees to find the optimal solution if time is not limited. But time needed for Simulated Annealing is too much and exact solution of NP-hard problems are still intractable. Properties of Simulated Annealing are that, it can be used as a heuristic to obtain near optimal solutions in limited time, and as the time limit is increased,

quality of the obtained solutions also increase. An important property of Simulated Annealing is the ability to escape from local minima if sufficient time is given. Simulated Annealing has been applied to various NP-hard optimization problem and for most problem it gives good results.

The subjects of this thesis is a recent algorithm, called Mean Field Annealing (MFA) was originally proposed for solving the traveling salesperson problem. MFA is general strategy and can be applied to various problem with suitable formulations. Work on MFA showed that, it can be successfully applied to combinatorial optimization problems. Mean Field Annealing (MFA) merges collective computation and annealing properties of Hopfield Neural Networks (HNN) and Simulated Annealing (SA), respectively, to obtain a general algorithm for solving combinatorial optimization problems. MFA can be used for solving a combinatorial optimization problem by choosing a representation scheme in which the final states of the spins can be decoded as a solution to the target problem. Then, an energy function is constructed whose global minimum value corresponds to the best solution of the problem to be solved. MFA is expected to compute the best solution to the target problem, starting from a randomly chosen initial state, by minimizing this energy function. In this thesis, MFA is formulated for the mapping problem in parallel processing and global routing problem in design automation of Field Programmable Gate Arrays.

The first combinatorial optimization problem, that is solved by MFA in this thesis, is global routing problem in design automation of field programmable gate arrays. This study investigates the routing problem in Static RAM Field Programmable Gate Arrays (FPGA's) implementing the non-segmented (Xilinx based) network [27]. As the routing in FPGA's is a very complex combinatorial optimization problem, routing process can be carried out in two phases : global routing followed by detailed routing [11]. Global routing determines the course of wires through sequences of channel segments. Detail routing determines the wire segment allocation for the channel segment routes found in the first phase which enable feasible switch box interconnection configurations [25, 14]. Global routing in FPGA can be done by using global routing algorithm proposed for standard cells [25]. LocusRoute global router is one of this type of router used for global routing in FPGA's [24] which divides the multi pin net's into two-pin net's and considers only minimum distance routes for these two-pin nets. The objective in the LocusRoute is to distribute the connections among channels so that channel densities are balanced. In this thesis, we propose a new approach the solution of global routing problem in FPGA's by using Mean Field Annealing technique.

Second problem that is solved by MFA is the *Mapping* problem [4, 8, 29]. The mapping problem arises as parallel programs are developed for distributed memory architectures. Various classes of problems can be decomposed into a set of interacting sequential subproblems (tasks) which can be executed in parallel. In these classes of problems, the interaction patterns among the tasks is static. In a distributed-memory architecture, a pair of processors communicate with each other over a shortest path of links connecting them. Hence, communication between each pair of processors can be associated with relative unit communication cost. Unit communication cost between a pair of processors can be assumed to be linearly proportional to the shortest path distance between those two processors. The objective in mapping subproblems to processors of multicomputers is the minimization of the expected execution time of the parallel program on the target architecture. Thus, the mapping problem can be modeled as an optimization problem by associating the following quality measures with a good mapping: (i) interprocessor communication overhead should be minimized, (ii) computational load should be uniformly distributed among processors in order to minimize processor idle time. The mapping problem has been solved by using Simulated Annealing, Kernighan-Lin type heuristic before. Also the MFA has been formulated in [6, 5]. But this formulation was a general formulation for any type of multicomputer whose intercommunication topologies are known. In this thesis we propose an efficient MFA formulation for topology-specific mapping for 2D-mesh and hypercube. For each interconnection topology, the efficient MFA formulation is given instead of using one general formulation as in [6].

In Chapter 2 the theory of the Mean Field Annealing heuristic and its encoding models are explained. The Field Programming Gate arrays, its design automation and Global Routing problem are introduced in Chapter 3. Also the FPGA model for global routing problem are proposed in this chapter. Chapter 4 gives the MFA formulation of global routing problem in FPGAs design automation. The mapping problem are introduced in Chapter 5. Chapter 6 presents general MFA formulation the topology-specific MFA formulation for Domain Mapping problem. Finally, conclusion of thesis are stated in Chapter 7.

#### Chapter 2

#### MEAN FIELD ANNEALING

In this chapter the Mean Field Annealing (MFA) heuristic is introduced and its models are given.

#### 2.1 Mean Field Annealing

Mean Field Annealing (MFA) merges collective computation and annealing properties of Hopfield Neural Networks (HNN) and Simulated Annealing (SA), respectively, to obtain a general algorithm for solving combinatorial optimization problems. HNN is used for solving various optimization problems and reasonable results are obtained for small size problems. However, simulations of this network reveals the fact that it is hard to obtain feasible solutions for large problem sizes. Hence, the algorithm does not have a good scaling property, which is a very important performance criterion for heuristic optimization algorithms. MFA is proposed as a successful alternative to HNN. In the MFA algorithm, problem representation is identical to HNN, but iterative scheme used to relax the system is different. MFA can be used for solving a combinatorial optimization problem by choosing a representation scheme in which the final states of the spins can be decoded as a solution to the target problem. Then, an energy function is constructed whose global minimum value corresponds to the best solution of the problem to be solved. MFA is expected to compute the best solution to the target problem, starting from a randomly chosen initial state, by minimizing this energy function. Steps of formulating MFA technique for a combinatorial optimization problem can be summarized as follows:

- Choose a representation scheme which encodes the configuration space of the target problem using spins. In order to get a good performance, number of possible configurations in the problem domain and the spin domain must be equal, i.e., there must be a one-to-one mapping between the configurations of spins and the problem.

- Formulate the cost function of the problem in terms of spins, i.e., derive the energy function of the system. Global minimum of the energy function should correspond to the global minimum of the cost function.

- Derive the mean field theory equations using this energy function, i.e., derive equations for updating expected values of spins.

- Minimize the complexity of update operations in order to get an efficient algorithm.

- Select the energy function and the cooling schedule parameters.

The MFA algorithm is derived by analogy to *Ising* and *Potts model* which are used to estimate the state of a system of particles, called spins, in thermal equilibrium.

#### 2.1.1 Ising Model

In Ising model spins can be in one of two states represented by 0 and 1. In the Ising model, the energy of a system with S spins has the following form:

$$H(\mathbf{s}) = \frac{1}{2} \sum_{k=1}^{S} \sum_{l \neq k} \beta_{kl} s_k s_l + \sum_{k=1}^{S} h_k s_k$$

(2.1)

Here,  $\beta_{kl}$  indicates the level of interaction between spins k and l, and  $s_k \in \{0, 1\}$  is the value of spin k. It is assumed that  $\beta_{kl} = \beta_{lk}$  and  $\beta_{kk} = 0$  for  $1 \le k, l, \le S$ . At thermal equilibrium, spin average  $\langle s_k \rangle$  of spin k can be calculated using Boltzmann distribution as follows

$$\langle s_k \rangle = \frac{1}{1 + e^{-\phi_k/T}} \tag{2.2}$$

Here,  $\phi_k = \langle H(\mathbf{s}) \rangle|_{s_k=0} - \langle H(\mathbf{s}) \rangle|_{s_k=1}$  represents the mean field effecting on spin k, where the energy average  $\langle H(\mathbf{s}) \rangle$  of the system is

$$\langle H(\mathbf{s}) \rangle = \sum_{k=1}^{S} \sum_{l \neq k} \beta_{kl} \langle s_k s_l \rangle + \sum_{k=1}^{S} h_k \langle s_k \rangle$$

(2.3)

The complexity of computing  $\phi_k$  using Eq.2.3 is exponential. However, for large number of spins, mean field approximation can be used to compute the energy average as

$$\langle H(\mathbf{s}) \rangle = \frac{1}{2} \sum_{k=1}^{S} \sum_{l \neq k} \beta_{kl} \langle s_k \rangle \langle s_l \rangle + \sum_{k=1}^{S} h_k \langle s_k \rangle$$

(2.4)

Since  $\langle H(\mathbf{s}) \rangle$  is linear in  $\langle s_k \rangle$ , mean field  $\phi_k$  can be computed using the following equation.

$$\phi_k = \langle H(\mathbf{s}) \rangle |_{s_k = 0} - \langle H(\mathbf{s}) \rangle |_{s_k = 1} = -\frac{\partial \langle H(\mathbf{s}) \rangle}{\partial \langle s_i \rangle} = -\left( \sum_{l \neq k} \beta_{kl} \langle s_l \rangle + h_k \right)$$

(2.5)

#### 2.1.2 Potts Model

In the Potts model, spins can be in one of the K states. In K state Potts model of S spins, the states of spins are represented using S K-dimensional vectors  $\mathbf{S_i} = [s_{i1}, \ldots, s_{ik}, \ldots, s_{iK}]^t$ ,  $1 \leq i \leq S$ , where "t" denotes the vector transpose operation.

The spin vector  $\mathbf{S_i}$  is allowed to be equal to one of the principal unit vectors  $\mathbf{e_1}, \dots, \mathbf{e_k}, \dots, \mathbf{e_K}$ , and can not take any other value. Principal unit vector  $\mathbf{e_k}$  is defined to be a vector which has all its components equal to 0 except its k'th component which is equal to 1. Spin  $\mathbf{S_i}$  is said to be in state k if it is equal to  $\mathbf{e_k}$ . Hence, a K state Potts spin  $\mathbf{S_i}$  is composed of K two state variables  $s_{i1}, \dots, s_{ik}, \dots, s_{iK}$ , where  $s_{ik} \in \{0, 1\}$ , with the following constraint

$$\sum_{k=1}^{K} s_{ik} = 1, \qquad 1 \le i \le S \tag{2.6}$$

In the Potts model, the energy of a system with S K-state Potts spin has the following form:

$$E(s) = \frac{1}{2} \sum_{i=1}^{S} \sum_{j \neq i} \beta_{ij} \mathbf{S}_i \mathbf{S}_j + \sum_{i=1}^{S} e_i \mathbf{S}_i$$

$$(2.7)$$

Here,  $\beta_{ij}$  indicate the level of interaction between spins i and j, and interaction between Potts spins  $\mathbf{S}_i\mathbf{S}_j$  is formulated as  $1/2\sum_{k=1}^K\sum_{l=1}^Ks_{ik}s_{jl}$ . Therefore we

can formulate the energy of the system as

$$E(s) = \frac{1}{2} \sum_{i=1}^{S} \sum_{j \neq i} \beta_{ij} 1/2 \sum_{k=1}^{K} \sum_{l=1}^{K} s_{ik} s_{jl} + \sum_{i=1}^{S} e_i \sum_{i=1}^{K} s_{ik}$$

(2.8)

Here,  $s_{ik} \in 0, 1$  is the value of kth state of the Potts spin i. At thermal equilibrium, spin average  $\langle s_{ik} \rangle$  of spin i can be calculated using Boltzmann distribution as follows

$$\langle s_{ik} \rangle = \frac{e^{\phi_{ik}/T}}{\sum_{l=1}^{K} e^{\phi_{il}/T}} \tag{2.9}$$

Here,  $\langle s_{ik} \rangle \in [0,1]$ . Note that  $s_{ik}$  can be 0 or 1 but  $\langle s_{ik} \rangle$  can be any real value between 0 and 1.  $\phi_{ik}$  represents the *mean field* effecting on state k of spin i. The mean field value for Potts spin i can be formulated as

$$\phi_{ik} = \langle E(\mathbf{s}) \rangle |_{\mathbf{S}_i = 0} - \langle H(\mathbf{s}) \rangle |_{\mathbf{S}_i = e_k}$$

(2.10)

$$= -\frac{\partial \langle H(\mathbf{s}) \rangle}{\partial \langle s_{ik} \rangle} = -\left(\sum_{j \neq i} \beta_{ij} \sum_{l=1}^{K} s_{jl} + h_i\right)$$

(2.11)

At each temperature, starting with initial spin averages, the mean field effecting on a randomly selected spin is found using Eqs. (2.5) and (2.10). Then, spin average is updated using Eq. (2.2) and Eq. (2.9) This process is repeated for a random sequence of spins until the system is stabilized for the current temperature. MFA algorithm tries to find equilibrium point of a system of S spins using annealing process similar to SA. The state equations used in MFA are isomorphic to the state equations of the neurons in the HNN. A synchronous version of MFA, can be derived by solving N difference equations for N spin values simultaneously. This technique is identical to the simulations of HNN done using numerical methods. Thus, evolution of a solution in a HNN is equivalent to the relaxation toward an equilibrium state affected by the MFA algorithm at a fixed temperature [9]. Hence MFA can be viewed as an annealed neural network derived from HNN. HNN and SA methods have a major difference: SA is an algorithm implemented in software, whereas HNN is derived with a possible hardware implementation in mind. MFA is somewhere in between, it is an algorithm implemented in software, having potential for hardware realization [8, 9]. In this work, MFA is treated as a software algorithm as SA. Results obtained are comparable to other software algorithms, conforming this point of view.

```

1.Get the Initial temperature T_0, and set T = T_0

2.Initialize spin averages

Ising spin: [\langle u_1 \rangle, \langle u_2 \rangle, \ldots]

Potts spins: [\langle \mathbf{S}_1 \rangle, \langle \mathbf{S}_2 \rangle, \ldots]

3.WHILE temperature T is in the cooling range DO

4.WHILE system is not stabilized for the current temperature DO

Select a spin i at random

4.1Compute mean field affecting on spin i

Ising spin: compute \phi_i = E(\mathbf{U})|_{u_i=0} - E(\mathbf{U})|_{u_i=1}

Potts spins: compute \phi_i = [\phi_{i1}, \phi_{i2}, \ldots, \phi_{iK}]^t such that

\phi_{ik} = E(\mathbf{S})|_{\mathbf{S}_i=\mathbf{0}} - E(\mathbf{S})|_{\mathbf{S}_i=\mathbf{e}_k} \text{ for } k = 1, 2, \ldots, K

4.2Update the average value of spin i

Ising spin: \langle u_i \rangle = e^{\phi_{i}/T}/(1 + e^{\phi_i/T})

Potts spin: \langle s_{ik} \rangle = e^{\phi_{ik}/T}/\sum_{l=1}^K e^{\phi_{il}/T} \text{ for } k = 1, 2, \ldots, K

5.Update T according to the cooling schedule

```

Figure 2.1. Mean Field Annealing Algorithm

#### 2.1.3 MFA Algorithm

The Mean Field Annealing algorithm are summarized in Figure 2.1.2. Beginning of the algorithm, the initial temperature are initialized and the current temperature is set to that initial value (step 1). After that Ising and Potts spins are initialized (step 2). Then, the annealing property of MFA are begin. In cooling schedule, the system tries to reach a stable state for each temperature until most of spins converges a stable state. For each temperature, while the system is not in stable state, a spin is selected randomly (step 4.1), and mean field values of spins are calculated (step 4.2) in order to update the spin values (step 4.3). When the system reaches the stable state, the temperature decreased by cooling schedule (step 5). At the end of algorithm, when most of spins converge, spins are decoded for a solution of target problem.

#### Chapter 3

#### FPGAs & GLOBAL ROUTING

This chapter introduces the Field Programmable Gate Arrays and its physical design automation steps briefly. Routing architectures of FPGA's are mentioned in this chapter and global routing problem and its previous solutions are given at the end of this chapter. Also the global routing problem in FPGAs is modeled in this chapter.

#### 3.1 Introduction to Field Programmable Gate Arrays

Field Programmable gate arrays (FPGAs) are new electrically programmable integrated circuits that provide high integration and rapid turnaround time. In VLSI design automation, the fabrication time is important problem. In order to reduce time to fabricate interconnects, programmable devices have been introduced. FPGA is very popular programmable devices used in ASIC design market.

FPGA can reduce manufacturing turnaround time and cost. In its simplest form, an FPGA consists of an array of programmable logic blocks and routing network to interconnect the logic blocks. The programmable logic blocks can be programmed by the user to implement a small logic function. An important property of FPGA is re-programmability by using electrically programmable switches. Commercial FPGA's differ in the type of programming technology used, in architecture of logic blocks and their routing architectures. An FPGA logic blocks can be as simple as transistor or as complex as a microprocessor.

It is typically capable of implementing many different combinational and sequential logic functions. FPGA's logic blocks can be classified as transistors pairs, basic small gates (such as two-input NAND's), multiplexes and Look-up tables.

#### 3.1.1 Logic Blocks

FPGAs logic blocks differ greatly in their size and implementation capability. The two transistor logic block can only implement an inverter but is very small in size, while look-up table logic blocks used in Xilinx FPGAs can implement any five-input logic function but they are significantly larger. Logic blocks can be classified in terms of granularity. Granularity can be defined in various ways, for example, as the number of boolean function that the logic block can implement, the number of equivalent two input NAND gates, total number of transistors, number of inputs and outputs. But generally, the commercial logic blocks can be classified into two categories: fine-grain and coarse-grain. Main advantage of using fine grain logic blocks is that the use-able blocks are fully utilized. However the main disadvantage of fine-grain blocks is that they require a relatively large number of wire segments and programmable switches.

#### 3.1.2 Programming Technologies

An FPGA is programmed using electrically programmable switches. According the properties of these programmable switches such as, on-resistance and capacitance, programming technologies can be classified into three main types. These three types are SRAM , antifuse and EPROM programming technologies.

The SRAM programming technologies uses static RAM cells to control the gates and multiplexes. In SRAM, the switch is a pass transistor controlled by the state of a SRAM bit. Therefore, SRAM is volatile. Hence The FPGA must be loaded and configured at the time of chip power-up, it requires external permanent memory to provide the programming bits such as PROM or EPROM. A major disadvantage of SRAM programming technology is its large area (its takes at least five transistors to implement an SRAM cell). However, SRAM programming technology has fast re-programmability as an advantage of it.

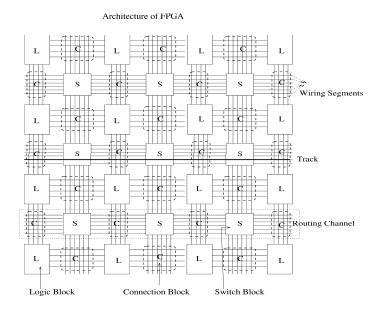

Figure 3.1. The Architecture of General FPGA

An antifuse is a two terminal device with an unprogrammed state presenting a very high resistance between its terminals. When a high voltage is applied across its terminals, the antifuse will blow and create low resistance link. This link is permanent. Programming an antifuse requires extra circuitry to deliver the high programming voltage and a high current. A major advantage of the antifuse is its small size. This advantage is reduced by the large size of the necessary programming transistors.

The floating gate programming technology uses technology found in ultraviolet erasable EPROM and electrically erasable EEPROM. Major advantage of EPROM technology is its fast reprogrammability. Also it does not require extra permanent memory to program the chip on power-up. However this technology increase the number of processing steps and high resistance transistors.

#### 3.1.3 Routing Architectures

The routing architecture of an FPGA is the manner in which the programmable switches and wiring segments are positioned to allow the programming interconnection of the logic. Figure 3.1 illustrates a typical routing architecture model. Before giving some commercial FPGA routing architecture, giving some definition is helpful for understand routing problem in FPGA. A wire

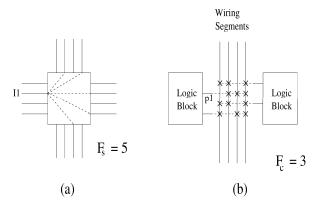

Figure 3.2. Example of flexibilities of FPGA (a) flexibility of switch block (b) flexibility of connection block

segment is a wire unbroken by programmable switches. One or more switches may attach to the wire segment. Each end of wire segment has a switch attached.

A *track* is sequence of one or more wire segments in a line.

A routing channel is group of parallel tracks as in Figure 3.1.

As shown in Figure 3.1, the model contains two basic structures: Connection blocks and switch blocks. A connection block provides connectivity from the input and output of logic blocks to the wire segments in the channels. A switch block provides connectivity between the horizontal as well as the vertical wire segments.

As in Figure 3.2, The general routing structure of FPGA has two important interconnection block. These are connection blocks which are used to make connections between logic block pin and routing segments, and switch blocks where connections are switched at the intersection of horizontal and vertical channels. The number of switching in connection and switch blocks is important for good routability. Large number of switching increase the routability but it causes poor performance and large delay and also large area.

The number and distribution of switches used in interconnection called flexibility of an FPGA. Flexibility of switch blocks  $(F_s)$  and flexibility of connection block  $(F_c)$  can be defined as the number of choices offered to each wire enter a switching block or a connection block, respectively. The flexibility of switch block  $F_s$  is defined to be total number of possible connection offered

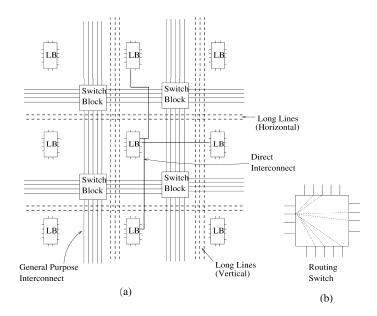

Figure 3.3. The Architecture of Xilinx 3000 FPGA

to each wire segment. The flexibility of connection block  $F_c$  is defined as the number of wires that each logical pin of logic block can connect. Next section describes the important routing architecture of commercial FPGA's such as Xilinx and Actel.

#### The Xilinx Routing Architecture

Figure 3.3 illustrates the routing architecture used in the Xilinx 3000 series FPGA. Connections are made from the logic block into the channel through a connection block. Since each connection site is large because of the SRAM programming technology, the Xilinx 3000 connection blocks connects each pin to only two or three out of five tracks passing by a block. On all four sides of the logic block there are connection blocks that connect a total of 11 different logic block pins to the wire segments. Once the logic pin is connected via the connections block makes connections between segments in intersecting horizontal and vertical channels. Each wire segment can connect to five or six out of a possible 15 wire segments on the opposites sides. There are four types of wire segments provided in the Xilinx 3000 architecture:

-General-purpose interconnect consisting of wire segments that pass through switches in the switch block.

Figure 3.4. The Architecture of Actel FPGA

- -Direct interconnect consisting of wire segments that connect each logic block output directly to four nearest neighbors.

- -Long lines, which span the length or width of the chip, providing high-fanout uniform delay connections.

- -Clock line, which is a single net that spans the entire chip and is driven by a high-drive buffer.

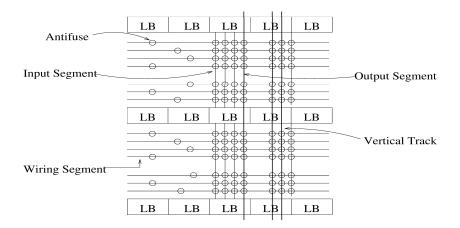

#### The Actel Routing Architecture

The Actel routing architecture has a asymmetric architecture because there are more general purpose tracks in horizontal direction than vertical direction. The connection block of the Actel routing architecture is shown in Figure 3.4. The connectivity of ACTEL FPGAs is different in input and output pins. For input pins, each pin can connect to all of the tracks in the channel that are on the same side as the pin. The output pins extend across two channels above the logic block and two channels below it. Output pins can connect to every track in all four channels that is crosses. There is no separable switch block in the Actel architecture. Instead, the switching is distributed throughout the horizontal channels. All vertical tracks can make a connection with every incident horizontal tracks. Each horizontal channel consists of 22 routing tracks, and each track is broken up into segments of different lengths. There are three type of vertical segments: input segments, output segments and freeways that either travel the entire height of chip, or some significant portion of it. This allows signal to travel longer vertical distance than permitted by output segments.

#### 3.2 Physical Design Automation of FPGAs

The physical design automation of FPGAs involves mainly three steps which include partitioning, placement and routing.

#### 3.2.1 Partitioning

Partitioning is the separation of the logic into Logic blocks. Partitioning has both a logical and physical component. The connections within a logic blocks are constrained by the limited routing architecture and limited number of blocks outputs. However, the quality of the resulting partitioning depends on how well the placement can be done. The logical component has been investigated in the context of technology mapping in logic optimization.

#### 3.2.2 Placement

Placement starts with logic blocks and input-output blocks in partitioned netlist and decides which corresponding blocks on the chip should contain them. The FPGA placement problem is very similar to traditional standard cell and gate array placement problems. Many of existing algorithm placement algorithms are applicable, such as simulated annealing, force directed relaxation and min-cut.

#### 3.2.3 Routing

After placement of all circuit, each pin of any multipoint net have to be connected. There are several routing algorithms for different kind of FPGA architectures and routing problem in FPGA's is very complex as in standard cells and gate arrays designs. Because of simplicity, the routing problem can be divided into two step as in traditional routing problem: global routing and detailed routing.

Global routing in FPGA's can be done by using a global router for standard cell design. In general such a global router divides the multipoint nets into two terminal nets and routes them with minimum distance path. While doing so it

Figure 3.5. General approach to FPGA routing a) Global routing b) Detailed routing

also tries to balance the density of channels. The global route defines a coarse route for each connection by assigning it a sequence of channel segments. After the paths are defined in terms of channel between two-pin connection detailed router chose specific wiring segments to implement the channel segment assigned during global routing.

### 3.3 Global Routing Problem in Design Automation of FPGAs

A global router chooses channels for each net and leaves the task of allocating specific wiring segments and switches to detailed router. The global routing in FPGA's decides for each net to determine which pins are actually to be connected. The objective of global router is to minimize the sum of the channel densities of all channels. As in many studies, the routing problem in FPGA is solved by directly allocating the segments and ignore the global routing phase. There are unique global router for FPGA: PGAroute. This global router similar the global router for standard cells and use the LocusRoute global routing algorithm.

In the LocusRoute algorithm, the following three steps are executed for each multi pin nets.

1) Net's Division: Each multi-pin net is divided into a set of two-pin connections using a minimum spanning tree algorithm.

Figure 3.6. Sample two bends routes

2) Route Generation and Evaluation: In this steps, the possible paths between each pin of two-pin nets are considered and evaluate this paths in terms of cost value and chose the lowest cost value path.

The method of choosing routes is based on paths that have two or less bends. LocusRoute evaluates a subnet of all two bend routes between the two physical pins and chose the one with the lowest cost. The cost function is defined in terms of the channel densities. Each wire segments and switch blocks are represented as elements of an array which is called as cost array. Each element of cost array  $H_{i,j}$  contains the number of routes that pass through the wire segment of (i, j). The cost of path(P) is calculated as

$$Cost(P) = \sum_{p} H_{i,j} \tag{3.1}$$

3)Reconstruction: This step joins all two-pin connections back together, performs assigns unique numbers to distinct segments of some nets in each channel.

Locus routes uses the iterative technique, that after the first time all nets are routed, each is sequentially ripped up and rerouted. Iterations reduces the order dependency and also it improves the routing quality.

#### 3.4 Model of FPGA for Global Routing

The form of commercial FPGA consists of a two dimensional regular array of programmable logic blocks (LB's), a programmable routing network and

Figure 3.7. The FPGA model used for Global Routing

switch boxes (SB's) [3, 1, 2]. Logic blocks are used to provide the functionality of a circuit. Routing network makes connections between LB's and input/output pads. Routing network of FPGA consists of wiring segments and connection blocks. Wiring segments have three type of routing resources in the commercial SRAM based FPGA [1]: channel segments, long lines and direct-interconnections. A horizontal (vertical) channel segment consists of a number of parallel wire segments connecting two successive SB's in a horizontal (vertical) channel. The SB's allow programmed interconnection between these channel segments. Direct-interconnection provides the connections between neighbor LB's. Long lines cross the routing area of FPGA vertically and horizontally. Connection blocks provide the connectivity from the input/output pins of LB's to the wiring segments of the respective channel segments. Each pin can be connected to a limited number of wiring segments in a channel and this is called as flexibility of connection block [16]. In this work, it is assumed that each LB pin can be connected to all wiring segments in the respective channels. Therefore, we can omit the connection block in our FPGA model.

Since the direct-interconnections are used by neighbor LB's to provide minimum propagation delay and the long lines are used by signals which must travel long distances (i.e., global clock), these interconnection resources are not considered in the global routing. Hence, our FPGA model for global routing considers only the LB's, SB's and channel segments. An FPGA can be modeled as a two dimensional array of LB's which are connected to the vertical and horizontal channel segments, and SB's which make connections between

Figure 3.8. (a) The routing area of the two-pin net and its subnets, (b) The possible routes for each subnets

the horizontal and vertical channel segments (Fig. 3.7).

In this work, we divide all multi-pin nets into two-pin nets using minimum spanning tree algorithm [19] as in LocusRoute. Hence, a net refers to a twopin net here, and hereafter. Consider the possible routings for a two-pin net with a Manhattan distance of  $d_h + d_v$  where  $d_h$  and  $d_v$  denote the horizontal and vertical distances, respectively, between the two pins of the net on the LB grid. The routing area of this net is restricted to a  $(d_h+1)\times(d_v+1)$  LB grid as shown in Fig. 3.8.a. Then, the shortest distance routing of this net can be decomposed into three *independent* routings as follows. Each pin of this net has only one neighbor SB in the optimal routing area. Hence, each pin can be connected to its unique neighbor SB either through a horizontal or a vertical channel segment (Fig. 3.8). Meanwhile, the optimal routing area for the connection of these two unique SB's is restricted to a  $d_h \times d_v$  SB grid embedded in the LB grid (Fig. 3.8). Hence, by exploiting this fact, we further subdivide each net into three two-pin subnets referred here as LS, SS and SL subnets (Fig. 3.8.b). Here, LS and SL subnets represent the LB-to-SB and SB-to-LB connections, respectively, and SS subnets represent the SB-to-SB connection for a particular net. Therefore, we consider only two possible routings for both LS and SL subnets and  $d_h + d_v - 2$  possible one or two bend routings for SS subnets for routing the original net.

We define an FPGA graph  $\mathbf{F}(L, S, C)$  for modeling the global routing problem in FPGAs. This graph is a  $P \times Q$  two-dimensional mesh where L, S and

Figure 3.9. The Cost Graph for FPGA model

C denote the set of LB's, SB's and channel segments, respectively. Here, P and Q is the number of horizontal and vertical channels in the FPGA. Each grid point (vertex)  $s_{pq}$  of the mesh represents the SB at horizontal channel p and vertical channel q. Each cell  $L_{pq}$  of the mesh represents the LB which is adjacent to four SB's  $s_{pq}$ ,  $s_{p,q+1}$ ,  $s_{p+1,q+1}$  and  $s_{p+1,q}$ . Edges are labeled such that the horizontal (vertical) edge  $c_{pq}^h$  ( $c_{pq}^v$ ) corresponds to the channel segment between the two consecutive SB's  $s_{pq}$  and  $s_{p,q+1}$  ( $s_{p+1,q}$ ) on the horizontal (vertical) channel p (q), respectively. Figure 3.9 displays a  $8 \times 6$  sample FPGA graph. Then, the pins of the LS/SL and SS type subnets are assigned to the respective cell-vertex and vertex-vertex pairs of the graph as is in mentioned earlier.

The global routing problem reduces to searching for most uniform possible distribution of the routes for these subnets. The uniform distribution of the routes is expected to increase the likelihood of finding a feasible routing in the following detailed routing phase. Hence, we need to define an objective function which rewards balanced routings. We associate weights with the edges of FPGA graph in order to simplify the computation of the balance quality of a given routing. The weight  $w_{pq}^h$  ( $w_{pq}^v$ ) of a horizontal (vertical) edge  $c_{pq}^h$  ( $c_{pq}^v$ ) denotes the density of the respective channel segment. Here, the density of a channel segment denotes the total number of nets passing through that segment for a given routing. Using this model, we can express the balance

quality B of a given routing  $\mathbf{R}$  as

$$B(\mathbf{R}) = \sum_{p=1}^{P} \sum_{q=1}^{Q-1} (w_{pq}^{h}(\mathbf{R}))^{2} + \sum_{q=1}^{Q} \sum_{p=1}^{P-1} (w_{pq}^{v}(\mathbf{R}))^{2}$$

(3.2)

As is seen in Eq. (3.2), each channel segment contributes the square of its density to the objective function thus penalizing imbalanced routing distributions. Hence, the global routing problem reduces to the minimization of the objective function given in Eq. (3.2).

#### Chapter 4

## MFA SOLUTION FOR GLOBAL ROUTING IN FPGA

This chapter investigates the routing problem in Static RAM Field Programmable Gate Arrays (FPGA's) implementing the non-segmented (Xilinx based) network [27]. The architecture model of FPGA used for formulation and Mean Field Annealing formulation for global routing problem are given in this chapter. Details of experiments, the circuits used in experiments and results are shown at the end of this chapter.

#### 4.1 MFA Formulation of Global Routing

The MFA algorithm is derived by analogy to *Ising* and *Potts* models which are used to estimate the state of a system of particles, called spins, in thermal equilibrium. In Ising model, spins can be in one of the two states represented by 0 and 1, whereas in Potts model they can be in one of the K states. All LS/SL subnets are represented by Ising spins since they have only two possible routes. In Ising spin encoding of each LS/SL subnet m,  $u_m = 1$  (0) denotes that the LB-to-SB or SB-to-LB routing is achieved through a single horizontal (vertical) channel segment. Each SS subnet n having  $K_n \geq 2$  possible routes is represented by a  $K_n$ -state Potts spin. The states of a  $K_n$ -state Potts spin is represented using a  $K_n$  dimensional vector

$$\mathbf{v}_{n} = [v_{n1}, \dots, v_{nr}, \dots, v_{n,K_{n}}]^{t}$$

(4.1)

where "t" denotes the vector transpose operation. Each Potts spin  $\mathbf{v}_n$  is allowed to be equal to one of the principal unit vectors  $\mathbf{e}_1, \ldots, \mathbf{e}_r, \ldots, \mathbf{e}_{K_n}$ , and can not take any other value. Principal unit vector  $\mathbf{e}_r$  is defined to be a vector which has all its components equal to 0 except its r'th component which is equal to 1. Potts spin  $\mathbf{v}_n$  is said to be in state r if  $\mathbf{v}_n = \mathbf{e}_r$ . Hence, a  $K_n$ -state Potts spin  $\mathbf{v}_n$  is composed of  $K_n$  two state variables  $v_{n1}, \ldots, v_{nr}, \ldots, v_{nK_n}$ , where  $v_{nr} \in \{0,1\}$ , with the following constraint

$$\sum_{r=1}^{K_n} v_{nr} = 1 (4.2)$$

If Potts spin n is in state r (i.e.,  $v_{nr} = 1$  for  $1 \le r \le K_n$ ) we say that the corresponding net n is routed by using the route r.

In the MFA algorithm, the aim is to find the spin values minimizing the energy function of the system. In order to achieve this goal, the average (expected) values  $\langle u_m \rangle$  and  $\langle \mathbf{v}_n \rangle = [\langle v_{n1} \rangle, \dots, \langle v_{nr} \rangle, \dots, \langle v_{nK_n} \rangle]^t$  of all Ising and Potts spins, respectively, are computed and iteratively updated until the system stabilizes at some fixed point. Note that for each Ising spin  $m, u_m \in \{0, 1\}$ , i.e.,  $u_m$  can take only two values 0 and 1, whereas  $\langle u_m \rangle \in [0, 1]$ , i.e.,  $\langle u_m \rangle$  can take any real value between 0 and 1. Similarly, for each Potts spin  $n, v_{nr} \in \{0, 1\}$  whereas  $\langle v_{nr} \rangle \in [0, 1]$ . When the system is stabilized,  $\langle u_m \rangle$  and  $\langle v_{nr} \rangle$  values are expected to converge to either 0 or 1 with the constraints  $\sum_{r=1}^{K_n} \langle v_{nr} \rangle = 1$  for the Potts spins.

In order to construct an energy function it is helpful to associate the following meaning to the values  $\langle u_m \rangle$  for LS/SL subnets.

$\langle u_m \rangle = \mathcal{P}(\text{subnet } m \text{ is routed by using the horizontal channel segment})$  $1 - \langle u_m \rangle = \mathcal{P}(\text{subnet } m \text{ is routed by using the vertical channel segment})$

That is,  $\langle u_m \rangle$  and  $1 - \langle u_m \rangle$  denote the probabilities of finding Ising spin m at states 1 and 0, respectively. In other words,  $\langle u_m \rangle$  and  $1 - \langle u_m \rangle$  denote the probabilities of routing subnet m through a single horizontal and vertical channel segment, respectively. Similarly, for SS subnets represented with Potts spins

$$\langle v_{nr} \rangle = \mathcal{P}(\text{subnet } n \text{ is routed through route r}) \quad \text{for} \quad 1 \le r \le K_n \quad (4.3)$$

That is,  $\langle v_{nr} \rangle$  denotes the probability of finding Potts spin at state r for  $1 \le r \le K_n$ . In other words,  $\langle v_{nr} \rangle$  denotes the probability of routing net n through

route r. Here and hereafter,  $u_m$  and  $v_{nr}$  will be used to denote the respective expected values ( $\langle u_m \rangle$  and  $\langle v_{nr} \rangle$ , respectively) for the sake of simplicity. Now, we formulate the total density cost of global routing problem as an energy term

$$E_{B}(\mathbf{U}, \mathbf{V}) = \sum_{p=1}^{P} \sum_{q=1}^{Q-1} [w_{pq}^{h}(\mathbf{U}) + w_{pq}^{h}(\mathbf{V})]^{2} + \sum_{q=1}^{Q} \sum_{p=1}^{P-1} [w_{pq}^{v}(\mathbf{U}) + w_{pq}^{v}(\mathbf{V})]^{2}$$

(4.4)

where

$$w_{pq}^{h}(\mathbf{U}) = \sum_{m \ni c_{pq}^{h}} u_{m} \text{ and } w_{pq}^{h}(\mathbf{V}) = \sum_{n \ni c_{pq}^{h}} \sum_{r \in R_{n}, r \ni c_{pq}^{h}} v_{nr}$$

$$w_{pq}^{v}(\mathbf{U}) = \sum_{m \ni c_{pq}^{v}} (1 - u_{m}) \text{ and } w_{pq}^{v}(\mathbf{V}) = \sum_{n \ni c_{pq}^{h}} \sum_{r \in R_{n}, r \ni c_{pq}^{v}} v_{nr}$$

where  $\mathbf{U} = \{u_1, u_2, \ldots\}$  and  $\mathbf{V} = \{\mathbf{v}_1, \mathbf{v}_2, \ldots\}$  represent the sets of Ising and Potts spins corresponding to the LS/SL and SS subnets, respectively. For LS/SL subnets, " $m \ni c_{pq}$ " denotes "for each LS/SL subnet m whose pair of pins share the horizontal or vertical channel segment  $c_{pq}$ ". For SS subnets " $n \ni c_{pq}$ " denotes "for each SS subnet n whose routing area contains the horizontal and vertical channel  $c_{pq}$ ". Furthermore, " $r \in R_n, r \ni c_{pq}$ " denotes "for each possible route r of SS subnet n which passes through the horizontal or vertical channel segment  $c_{pq}$ ". Here,  $w_{pq}(\mathbf{U})$  and  $w_{pq}(\mathbf{V})$  represent the probabilistic densities of the horizontal or vertical channel segment  $c_{pq}$  for the current routing states of LS/SL and SS subnets, respectively. Hence,  $w_{pq}(\mathbf{U}, \mathbf{V}) = w_{pq}(\mathbf{U}) + w_{pq}(\mathbf{V})$  represents the total probabilistic density of horizontal or vertical channel segment  $c_{pq}$  for the overall current routing state.

Mean field theory equations, needed to minimize the energy function  $E_B$ , can be derived as

$$\phi_m(\mathbf{U}, \mathbf{V}) = E_B(\mathbf{U}, \mathbf{V})|_{u_m=0} - E_B(\mathbf{U}, \mathbf{V})|_{u_m=1}$$

$$= -2[w_{pq}^h(\mathbf{U}, \mathbf{V}) - w_{pq}^v(\mathbf{U}, \mathbf{V}) - 2(u_m - 0.5)] \qquad (4.5)$$

where  $c_{pq}^h, c_{pq}^v \in m$

for an Ising spin m and

$$\phi_{nr}(\mathbf{U}, \mathbf{V}) = E_B(\mathbf{U}, \mathbf{V})|_{\mathbf{v}_n = 0} - E_B(\mathbf{U}, \mathbf{V})|_{\mathbf{v}_n = e_r}$$

$$= -2\left[\sum_{c_{pq}^h \in r} (w_{pq}^h(\mathbf{U}, \mathbf{V}) - v_{nr}) + \sum_{c_{pq}^v \in r} (w_{pq}^v(\mathbf{U}, \mathbf{V}) - v_{nr})\right]$$

for  $1 \le r \le K_n$  (4.6)

for a Potts spin n, respectively. Mean field values  $\phi_m$  and  $\phi_{nr}$  can be interpreted as the increases in the energy function  $E_B(\mathbf{U}, \mathbf{V})$  when Ising and Potts spins m and n are assigned to states 1 and r, respectively. Hence,  $-\phi_m$  and  $-\phi_{nr}$

may be interpreted as the decreases in the overall solution qualities by routing LS/SL and SS subnets m and n through the horizontal channel and route r, respectively. Then,  $u_m$  and  $v_{nr}$  values are updated such that probabilities of routing subnets m and n through horizontal channel and route r increase with increasing mean field values  $\phi_m$  and  $\phi_{nr}$  as follows:

$$u_m = \frac{e^{\phi_m/T}}{1 + e^{\phi_m/T}} \tag{4.7}$$

$$u_{m} = \frac{e^{\phi_{m}/T}}{1 + e^{\phi_{m}/T}}$$

$$v_{nr} = \frac{e^{\phi_{nr}/T}}{\sum_{k=1}^{K_{n}} e^{\phi_{nk}/T}} \quad \text{for} \quad r = 1, 2, \dots, K_{n}$$

$$(4.7)$$

respectively.

After the mean field equations (Eqs. (4.5-4.6)) are derived, the MFA algorithm can be summarized as follows. First, an initial high temperature spin average is assigned to each spin, and an initial temperature T is chosen. Each  $u_m$  value is initialized to  $0.5 \pm \delta_m$  and each  $v_{nr}$  value is assigned to  $1/K_n \pm \delta_{nr}$ where  $\delta_m$  and  $\delta_{nr}$  denote randomly selected small disturbance values. Note that  $\lim_{T\to\infty} u_m = 0.5$  and  $\lim_{T\to\infty} v_{nr} = 1/K_n$ . In each MFA iteration, the mean field effecting a randomly selected spin is computed using either Eq. (4.5) or Eq. (4.6). Then, the average of this spin is updated using either Eq. (4.7) or Eq. (4.8). This process is repeated for a random sequence of spins until the system is stabilized for the current temperature. The system is observed after each spin update in order to detect the convergence to an equilibrium state for a given temperature. If energy function  $E_B$  does not decrease in most of the successive spin updates, this means that the system is stabilized for that temperature. Then, T is decreased according to a cooling schedule, and iterative process is re-initialized. At the end of this cooling schedule, each Ising spin m is set to state 1 if  $u_m \geq 0.5$  or to state 0, otherwise. Similarly, maximum element in each Potts spin vector is set to 1 and all other element are set to 0. Then, the resulting global routing is decoded as mentioned earlier.

#### 4.2Implementation

The performance of the proposed MFA algorithm for the global routing problem is evaluated in comparison with the well-known LocusRoute algorithm [24].

The MFA global router is implemented efficiently as described in Section 4.1. Average of each Ising spin m is initialized by randomly selecting  $u_m^{init}$

in the range  $0.45 \leq u_m \leq 0.55$ . Similarly, average of each Potts spin n is initialized by randomly selecting  $K_n$   $v_{nr}$  values in the range  $0.9/K_n \leq v_{nr} \leq 1.1/K_n$  and normalizing  $v_{nr}^{init} = v_{nr} / \sum_{k=1}^{K_n} v_{nk}$  for  $r = 1, 2, ..., K_n$ . Note that random selections are achieved by using uniform distribution in the given ranges.

The initial temperature parameter used in mean field computation is estimated using the initial spin averages values. Selection of initial temperature parameters  $T_0$  is crucial to obtain good routing. In previous applications of MFA, it is experimentally observed that spin averages tend to converge at a critical temperature. Although there are some methods proposed for the estimation of critical temperature, we prefer an experimental way for computing  $T_0$  which is easy to implement and successful as the results of experiments indicate. We compute the initial average mean field as

$$\phi_{avg}^{init} = \left(\sum_{m=1}^{N_m} \phi_m^{init} + \sum_{n=1}^{N_n} \sum_{k=1}^{K_n} \phi_{nr}^{init}\right) / (N_m + \sum_{n=1}^{N_n} K_n)$$

Note that initial mean field values  $\phi_m^{init}$  and  $\phi_{nr}^{init}$  are computed according to Eqs. (4.5) and (4.6) using initial spin values  $u_m^{init}$  and  $v_{nr}^{init}$ . Here,  $N_m$  and  $N_n$  denote the total number of Ising and Potts spins, respectively, where  $N = N_m + N_n$  denotes the total number of spins (subnets). Then, initial temperature is computed as  $T_0 = C\phi_{avg}^{init}$  where constant C is chosen as 540 for all experiments.

The cooling schedule is an important factor in the performance of MFA global router. For a particular temperature, MFA proceeds for randomly selected unconverged net spin updates until  $\Delta E < \epsilon$  for M consecutive iterations respectively where M=N initially and  $\epsilon=0.05$ . Average spin values are tested for convergence after each update. For an Ising spin m, if either  $u_m \leq 0.05$  or  $u_m \geq 0.95$  is detected, then spin m is assumed to converge to state 0 or state 1, respectively. For a Potts spin n, if  $v_{nr} \geq 0.95$  is detected for a particular  $r = 1, 2, ..., K_n$ , then spin n is assumed to converge to state r. The cooling process is realized in two phases, slow cooling followed by fast cooling, similar to the cooling schedules used for Simulated annealing. In the slow cooling phase, temperature is decreased by  $T = \alpha \times T$  where  $\alpha = 0.9$ until  $T < T_0/1.5$ . Then, in the fast cooling phase, M is set to M/2,  $\alpha$  is set to 0.8. Cooling schedule continues until 90% of the spins converge. At the end of this cooling process, each unconverged Ising spin m is assumed to converge to state 0 or state 1 if  $u_m < 0.5$  or  $u_m \ge 0.5$ , respectively. Similarly, each unconverged Potts spin n is assumed to converge to state r where  $v_{nr} = \max\{v_{nk}: k = 1, 2, \dots, K_n\}$ . Then, the result is decoded as described in Section 4.1, and the resulting global routing is found.

| Benchmarks |              |              |              |  |  |  |  |  |  |

|------------|--------------|--------------|--------------|--|--|--|--|--|--|

|            | Circuits     |              |              |  |  |  |  |  |  |

| name       | number<br>of | number<br>of | FPGA<br>size |  |  |  |  |  |  |

|            | nets         | 2-pin nets   |              |  |  |  |  |  |  |

| 9symml     | 71           | 259          | 10x9         |  |  |  |  |  |  |

| too-large  | 177          | 519          | 14x13        |  |  |  |  |  |  |

| apex7      | 124          | 300          | 11x9         |  |  |  |  |  |  |

| example 2  | 197          | 444          | 13x11        |  |  |  |  |  |  |

| vda        | 216          | 722          | 16x15        |  |  |  |  |  |  |

| alu2       | 137          | 511          | 14x12        |  |  |  |  |  |  |

| alu4       | 236          | 851          | 18x16        |  |  |  |  |  |  |

| term1      | 87           | 202          | 9x8          |  |  |  |  |  |  |

| C1355      | 142          | 360          | 12x11        |  |  |  |  |  |  |

| C499       | 142          | 360          | 12x11        |  |  |  |  |  |  |

| C880       | 173          | 427          | 13x11        |  |  |  |  |  |  |

| K2         | 388          | 1256         | 21x19        |  |  |  |  |  |  |

| Z03D4      | 575          | 2135         | 26x25        |  |  |  |  |  |  |

| buscntl    | 145          | 392          | 12x11        |  |  |  |  |  |  |

| dramfsm    | 389          | 1422         | 22x21        |  |  |  |  |  |  |

| dma        | 197          | 771          | 17x15        |  |  |  |  |  |  |

| z03        | 575          | 2135         | 26x25        |  |  |  |  |  |  |

Table 4.1. MCNC benchmark circuits used in experiments

The LocusRoute algorithm is implemented as in [24]. As the LocusRoute depends on rip-up and reroute method, LocusRoute is allowed to reroute the circuits 5 times. No bend reduction has been done as in [3]. Both algorithms are implemented in the C programming language.

## 4.3 Experimental Results

This section presents experimental performance evaluation of the proposed MFA algorithm in comparison with LocusRoute and Simulated Annealing (SA) algorithm. All algorithms are tested for the global routing of thirteen ACM SIGDA Design Automation benchmarks (MCNC) and four famous FPGA benchmark circuits on SUN SPARC 10. The Table 4.1 illustrates the properties of these benchmark circuits.

These three algorithms yield the same total wiring length for global routing since two or less bend routing scheme is adopted in all of them. Necessary design automation process such as technology mapping and placement are done in University of Toronto by using Chortle technology mapper [11] and XAltor placement tools.

| Circuit     | MFA  |      |              | PGA   |      |      | SA    |      |         |

|-------------|------|------|--------------|-------|------|------|-------|------|---------|

|             | Cost | Dens | $_{ m time}$ | Cost  | Dens | time | Cost  | Dens | time    |

| 9symml      | 1.0  | 12.0 | 0.36         | 1.032 | 14   | 0.00 | 1.000 | 12.0 | 20.64   |

| toolarge    | 1.0  | 16.0 | 0.88         | 1.071 | 17   | 0.06 | 1.003 | 16.0 | 113.90  |

| apex7       | 1.0  | 14.0 | 0.42         | 1.073 | 16   | 0.00 | 0.935 | 14.0 | 31.46   |

| example 2   | 1.0  | 15.0 | 0.64         | 1.097 | 16   | 0.02 | 0.856 | 15.0 | 76.54   |

| vda         | 1.0  | 17.0 | 0.42         | 1.055 | 18   | 0.10 | 1.002 | 17.0 | 207.80  |

| alu2        | 1.0  | 17.0 | 0.30         | 1.080 | 17   | 0.02 | 0.928 | 17.0 | 91.44   |

| alu4        | 1.0  | 17.0 | 0.68         | 1.073 | 19   | 0.10 | 0.966 | 17.0 | 288.78  |

| term1       | 1.0  | 14.0 | 0.34         | 1.093 | 14   | 0.00 | 0.921 | 14.0 | 13.28   |

| C1355       | 1.0  | 13.0 | 0.56         | 1.119 | 15   | 0.00 | 1.000 | 13.6 | 50.36   |

| C499        | 1.0  | 15.0 | 0.48         | 1.075 | 16   | 0.00 | 1.003 | 15.0 | 44.58   |

| C880        | 1.0  | 15.4 | 0.68         | 1.065 | 17   | 0.04 | 0.933 | 16.8 | 74.40   |

| k2          | 1.0  | 20.2 | 0.94         | 1.038 | 22   | 0.20 | 0.952 | 20.0 | 712.10  |

| z03D4       | 1.0  | 17.0 | 2.34         | 1.117 | 18   | 0.30 | 1.000 | 17.0 | 1821.12 |

| buscntl     | 1.0  | 13.0 | 0.42         | 1.050 | 13   | 0.00 | 0.998 | 13.0 | 54.92   |

| dramfsm     | 1.0  | 15.0 | 1.94         | 1.073 | 18   | 0.20 | 0.999 | 15.0 | 763.02  |

| dma         | 1.0  | 15.0 | 1.96         | 1.084 | 16   | 0.10 | 0.972 | 15.0 | 216.80  |

| <i>z</i> 03 | 1.0  | 20.0 | 2.10         | 1.119 | 21   | 0.30 | 1.000 | 20.0 | 1837.86 |

Table 4.2. The Global Router results

Table 4.2 illustrates the performance results of these three algorithms for the benchmark circuits. The MFA algorithm is executed 10 times for each circuit starting from different, randomly chosen initial configurations. The results given for the MFA algorithm in Table 4.2 illustrate the average of these executions. Global routing cost values of the solutions found by both algorithms are computed using Eq. (3.2) and then normalized with respect to those of MFA. In Table 4.2, maximum channel density denotes the number of routes assigned to the maximally loaded channels. That is, it denotes the minimum number of tracks required in a channel for 100% routability.

As is seen in Table 4.2, global routing costs of the solutions found by MFA are 3.1%-10.5% better than those of LocusRoute. As is also seen in this table, maximum channel density requirements of the solutions found by MFA are less than those of LocusRoute in almost all circuits except *alu2* and *term1*. Both algorithms obtain the same maximum channel density for these two circuit.

How the global router distributes the channel densities, how the global router decrease the maximum channel densities and how detailed router completes the routing are some important metrics to measure the quality of the global routers. The propagation net delays, number of switch used, number of tracks in a channel are considered in comparison of global routers after completion of routing. The channel densities distribution affects on the number of tracks and switch also the propagation delay (because of number of switches) of the nets. In next paragraphs, the results of global routes are given in terms

|          |      | Ro                  | uting In | nfo.       |     | Delay Info. |            |       |        |        |

|----------|------|---------------------|----------|------------|-----|-------------|------------|-------|--------|--------|

| Circuit  | Tot  | otal Segment Shared |          | Avg. Delay |     |             | Max. Delay |       |        |        |

|          | MFA  | PGA                 | Imp      | MFA        | PGA | MFA         | PGA        | Imp   | MFA    | PGA    |

| 9symml   | 674  | 711                 | 5.20     | 42         | 85  | 5.06        | 5.56       | 9.01  | 63.38  | 57.97  |

| toolg    | 1803 | 1951                | 7.59     | 47         | 114 | 13.83       | 15.10      | 8.45  | 125.48 | 122.80 |

| apex7    | 960  | 1026                | 6.43     | 36         | 63  | 9.88        | 10.64      | 7.15  | 70.97  | 77.65  |

| exp2     | 1775 | 1893                | 6.23     | 42         | 56  | 10.08       | 11.98      | 15.86 | 101.31 | 121.88 |

| vda      | 2760 | 2950                | 6.44     | 70         | 176 | 18.67       | 20.58      | 9.30  | 140.77 | 170.36 |

| alu2     | 1580 | 1674                | 5.62     | 36         | 129 | 9.82        | 9.61       | -2.12 | 129.24 | 110.30 |

| alu4     | 3183 | 3424                | 7.04     | 67         | 203 | 16.58       | 17.08      | 2.93  | 153.88 | 163.30 |

| term1    | 602  | 638                 | 5.64     | 21         | 47  | 9.57        | 9.60       | 0.32  | 74.81  | 70.50  |

| C1355    | 1299 | 1347                | 3.56     | 27         | 82  | 12.17       | 13.15      | 7.50  | 121.01 | 118.12 |

| C499     | 1242 | 1296                | 4.17     | 37         | 82  | 11.64       | 12.02      | 3.15  | 79.75  | 94.46  |

| C880     | 1575 | 1670                | 5.69     | 38         | 91  | 14.83       | 15.36      | 3.48  | 111.58 | 115.72 |

| K2       | 5980 | 6323                | 5.42     | 88         | 306 | 25.77       | 27.54      | 6.43  | 244.35 | 229.54 |

| Z03D4    | 7125 | 7700                | 7.47     | 227        | 555 | 12.75       | 13.60      | 6.26  | 190.62 | 191.65 |

| bus-cntl | 1128 | 1213                | 7.01     | 43         | 94  | 7.94        | 8.57       | 7.28  | 104.36 | 126.24 |

| dram-fsm | 4267 | 4648                | 8.20     | 174        | 403 | 6.19        | 6.68       | 7.35  | 140.61 | 157.05 |

| dma      | 2300 | 2545                | 9.63     | 94         | 214 | 15.17       | 16.58      | 8.53  | 200.82 | 194.71 |

| z03      | 7161 | 7870                | 9.01     | 267        | 533 | 13.05       | 14.40      | 9.39  | 193.18 | 192.93 |

Table 4.3. The SEGA detailed routing results in area optimization mode

of these metrics. The balance cost of SA and MFA global routers are not very different but the execution time of SA is 250 times longer than the MFA on the averages for all circuit.

The detailed router used in this experiments is called SEGA [20], for SEGment Allocator, and was developed specifically for SRAM based FPGA's. The input of SEGA is a netlist of two point connections, which is output of the global router. To route the connections, SEGA allocates wire segments according to cost function, basing its decisions on either of two goals: optimize for area or optimize for speed. For area optimization, only routability of the circuit is considered, which means the cost function focuses only on the task of successfully routing 100% of the connections in a circuit. In delay optimization, SEGA selects the routes that have the best speed performance. The following assumption are done in experiments. All routing channels have an equal number of tracks. The flexibility of the channel blocks are equal to number of tracks. (Each logic pin can connect to a channel with all tracks) The LocusRoute global routing algorithm used in PgaRoute global router (PGA). For further part of this chapter, PGA global router are used for LocusRoute algorithm [23].

The SEGA detailed router routes the nets by considering either area optimization or speed optimization criteria. Therefore all circuits are tested according to these two optimization criteria, separately. The output of MFA and

|             |      | Ro      | outing In     | ıfo. |            |       |       | Delay In:  | fo.    |        |

|-------------|------|---------|---------------|------|------------|-------|-------|------------|--------|--------|

| Circuit     | Tot  | al Segm | egment Shared |      | Avg. Delay |       |       | Max. Delay |        |        |

|             | MFA  | PGA     | Imp           | MFA  | PGA        | MFA   | PGA   | Imp        | MFA    | PGA    |

| 9symml      | 653  | 649     | -0.62         | 63   | 147        | 5.07  | 5.28  | 3.94       | 56.46  | 48.67  |

| toolg       | 1776 | 1822    | 2.52          | 74   | 243        | 13.34 | 13.06 | -2.17      | 128.56 | 106.00 |

| apex7       | 942  | 952     | 1.05          | 54   | 137        | 9.73  | 9.86  | 1.28       | 70.97  | 63.32  |

| exp2        | 1746 | 1762    | 0.91          | 71   | 187        | 10.01 | 10.81 | 7.40       | 95.27  | 98.10  |

| vda         | 2704 | 2774    | 2.52          | 126  | 352        | 19.07 | 19.10 | 0.17       | 148.30 | 164.71 |

| alu2        | 1533 | 1542    | 0.58          | 83   | 261        | 9.46  | 9.56  | 1.07       | 127.29 | 128.45 |

| alu4        | 3132 | 3193    | 1.91          | 118  | 434        | 16.17 | 16.29 | 0.76       | 145.32 | 147.41 |

| term1       | 591  | 592     | 0.17          | 32   | 93         | 9.74  | 8.13  | -19.82     | 76.82  | 46.33  |

| C1355       | 1277 | 1269    | -0.63         | 49   | 160        | 12.34 | 11.69 | -5.59      | 126.73 | 98.27  |

| C499        | 1225 | 1222    | -0.25         | 54   | 156        | 11.66 | 10.72 | -8.81      | 81.49  | 83.71  |

| C880        | 1552 | 1567    | 0.96          | 61   | 194        | 14.39 | 14.01 | -2.73      | 106.94 | 106.06 |

| K2          | 5900 | 5995    | 1.58          | 168  | 634        | 27.05 | 26.50 | -2.10      | 262.23 | 210.25 |

| Z03D4       | 6965 | 7664    | 9.12          | 437  | 1191       | 12.42 | 12.34 | -0.65      | 167.32 | 169.05 |

| bus-cntl    | 1112 | 1114    | 0.18          | 59   | 193        | 8.03  | 7.95  | -1.04      | 95.93  | 86.24  |

| dram-fsm    | 4155 | 4305    | 3.48          | 286  | 746        | 6.05  | 6.61  | 8.54       | 140.61 | 146.57 |