# Using Planes of Optoelectronic Devices Interconnected by Free-Space Optics: Systems Issues and Application Opportunities

Haldun M. Ozaktas Bilkent University Department of Electrical Engineering TR-06533 Bilkent, Ankara, Turkey

This work was originally prepared as an AT&T Bell Laboratories Technical Memorandum number BLO111680-940922-57TM dated September 22, 1994, and released for publication on May 7, 1996.

#### Abstract

The design of a computing machine takes place at several levels of abstraction ranging from materials and device engineering to system architecture to high level software. This system of levels of abstraction enables the design problem to be broken down into manageable subproblems, much as in a procedural programming language. On the other hand, it makes difficult the introduction of novel concepts and technologies such as optoelectronic device planes ("smart pixels"), which do not readily fit in the existing scheme of things. We try to develop an understanding of this system of levels of abstraction, why and how it resists the introduction of optical technology, and how one can modify it so as to successfully house optical technology. We argue that in the near future, optoelectronic technology can be successfully introduced if: i) changing technology or applications create a significant bottleneck in the existing system of levels of abstraction that can be removed by the introduction of optical technology (e.g. interconnections, memory access); ii) special purpose applications involving very few levels of abstraction can be identified (e.g. sensing, image processing); iii) it is possible to modify a few levels of abstraction above the level that optical technology is introduced, so that the optical technology is smoothly "grafted" to the existing system of levels of abstraction (e.g. modifying communications schemes or standards so as to match the capabilities of optical switching systems, employing parallel architectures to match the parallel flow of information generated by optical subsystems).

Hybrid integration of self-electrooptic effect devices on silicon integrated circuits is a promising optoelectronic device plane technology in which an array of optical "pinouts" is provided for the electronic circuits. Free-space optical interconnection technology allows these planes to be connected in a variety of ways. Among these, the multistage architecture is found to have many desirable features, but many alternatives remain unexplored.

Image processing is a significant application area in which optoelectronic technology can have a significant impact because the two-dimensional nature of the data, the global nature of important classes of operations, and the need for real-time pipelining and/or iterative processing naturally match physical architectures that can be efficiently implemented. Image processing operations are often classified by application. After reviewing these, we provide a classification based on the information flow required to realize these operations. Different degrees of information flow require different kinds of connections. By comparison with recently developed multiple active layer electronic technology, we argue that optoelectronic technology offers an advantage when a global pattern of connections is necessary.

We identify several tradeoffs and system level considerations which have not yet been fully clarified. One of these is the issue of trading speed for resolution; that is, using spatial multiplexing techniques to process larger images. Another is the issue of how to successfully assemble many device planes in parallel so as to be able to construct larger systems. We believe that it is important to break the limits imposed by a single optical aperture or a single chip.

Optoelectronic systems such as memory with parallel access, state machines, matrix processors, neural networks, etc. may represent more realistic challenges as compared to general purpose systems, for short term development and validation of optoelectronic device plane technologies. These systems do not involve too many levels of abstraction (which makes their conception possible), often involve regular patterns of information flow (which leads to simple physical architectures), and usually result in an interconnection bottlenecked system when implemented with purely electronic technologies. The major challenge with such a system is to either successfully interface it as a subsystem of a larger (possibly general purpose) system in a way that benefits from its high performance, or to find a special purpose application where it can directly exhibit its high performance.

We identify and define two directions for further research which we believe are worth investigating not only for their own sake, but also because they will provide a platform on which several system level issues can be clarified and the optoelectronic technology validated. The first is an optically interconnected multiprocessor computer. Although this is not a new idea, SEED on silicon technology makes it particularly attractive. The second is a multistage programmable iterative real-time image processor. The strength of this concept lies in the excellent mapping of computational requirements onto a physically convenient architecture.

## Contents

| 1  | Introduction                                                                                                                                                                                                                                                                                                              | 2                                      |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 2  | Introducing optical technology into computing machinery  2.1 Levels of abstraction in problem solving                                                                                                                                                                                                                     | 2<br>2<br>3<br>4<br>5<br>8             |

| 3  | Optoelectronic integration technology 3.1 Hybrid integration of SEED devices with silicon 3.2 Free-space optical interconnections 3.3 Heat removal considerations 3.4 Physical architectures for optoelectronic systems 3.5 How much silicon per optical pixel? 3.6 Analog versus digital 3.7 Prospects of the technology | 8<br>10<br>10<br>10<br>12<br>12<br>12  |

| 4  | General purpose systems                                                                                                                                                                                                                                                                                                   | 13                                     |

| 5  |                                                                                                                                                                                                                                                                                                                           | 13<br>14<br>15<br>15                   |

| 6  | v i                                                                                                                                                                                                                                                                                                                       | 15<br>16<br>16<br>17<br>18             |

| 7  | Special purpose systems: sensing and display                                                                                                                                                                                                                                                                              | 19                                     |

| 8  | Quasi-general purpose processors or coprocessors8.1Memory with parallel access8.2Combinatorial logic units and finite state machines8.3Matrix-vector multipliers and matrix processors8.4Neural networks8.5Cellular automata8.6Subsystems with few inputs and outputs                                                     | 20<br>20<br>20<br>21<br>21<br>21<br>22 |

| 9  | Some system level issues  9.1 Trading speed for resolution                                                                                                                                                                                                                                                                | 22<br>22<br>22<br>23                   |

| 10 | Directions for development  10.1 Optically interconnected parallel computers                                                                                                                                                                                                                                              | 23<br>23<br>24                         |

| 11 | Conclusions                                                                                                                                                                                                                                                                                                               | <b>25</b>                              |

### 1 Introduction

The integration of larger numbers of primitive computing elements (switches, transistors, gates, processors, etc.) to produce computers of greater processing power requires the use of interconnections with greater length/width ratios.<sup>1</sup>

As the length of an interconnection is increased, the time it takes for a signal to propagate to the other end also increases, at least as much as dictated by the speed of light. While this limitation holds for all types of interconnections, normally conducting electrical interconnections have much more severe limitations. The signal delay is a quadratic function of the length/width ratio beyond a certain length/width ratio, since the line becomes too lossy to allow pulse propagation. The energy per transmitted bit also increases with line length, even when repeaters are used [5, 6].

For these and other reasons<sup>2</sup> that have been extensively discussed in previous work, it has been suggested to use optical interconnections for implementing the longer connections in computing systems, especially when an electrical line to be used instead would have a high length/width ratio. (See [1, 2, 3, 4, 5, 6, 7, 8, 9, 10] and the references therein.)

Here we discuss various architectural and application oriented issues within the framework of a particular technology allowing hybrid integration of optical and electronic devices, namely flip-chip bonding of self-electrooptic effect devices (SEED's) on silicon [11]. Our discussions will mostly be of a sufficiently general nature to be applicable to other similar technologies in which optical inputs and outputs can be distributed essentially arbitrarily over electronic circuits manufactured under a mature platform (such as CMOS).

This is a working document so that the degree of completeness and refinement of the various sections is not uniform. Also, the various categories, classification schemes, and terminology introduced is not definite and subject to improvement.

## 2 Introducing optical technology into computing machinery

#### 2.1 Levels of abstraction in problem solving

A lot of attention has been paid to determining at what level of the interconnection hierharchy optics should be employed (board to board? chip to chip? etc.). On the other hand, it seems that little attention has been paid to the issue of determining at what level of abstraction of the computational process optics should be introduced.<sup>3</sup>

To understand what this means, let us reflect on how one usually accomplishes a task by using a computer. Say that we wish to modify a high resolution image in some way so that it is more pleasing to the eye. It might be possible to come up with certain operations involving convolutions, matrix operations etc. that enable us to do this. These mathematical operations will have to be broken down into repetitive or recursive sequences of more elementary operations. In doing this, we will have developed an algorithm for solving the problem. The algorithm will be written down in the form of a high level programming language, which will be translated into assembly language, which will be run by a microprocessor, which is essentially a high level logic system, which is made up of lower level logic functions (such as shift, add, etc.), which are made of gates, which are made of transistors.

Given a certain number of transistors or logic gates, there is no reason to think that this way of doing image enhancement is optimal, but at least it is possible. Realization of the techniques associated with each level of abstraction can be posed as self-contained problems which can be solved by specialists, with some care being necessary to ensure successful interface to the levels immediately above and below. Some

<sup>&</sup>lt;sup>1</sup>This can be avoided by resorting to architectures with local connections only, but for problems which intrinsically require global flow of information this merely amounts to breaking down the necessary long distance communication paths into a large number of short hops, which is not necessarily optimal [9].

<sup>&</sup>lt;sup>2</sup>E.g., the possibility of nonplanar interconnections, voltage isolation, very little or no frequency dependent crosstalk and distortion, no impedance matching problems even with multiple taps, etc.

<sup>&</sup>lt;sup>3</sup>It will be evident that the two issues are not unrelated, the levels of abstraction to some degree corresponding to the levels in the packaging hierarchy.

degree of optimization within each level is usually performed, but it is often not possible to optimize over several levels. No central committee has ever decided on what these levels of abstraction are either; they are the outcome of historical developments.

Device physicists try to minimize the switching time and energy, and computer scientists try to minimize the consecutive number of steps required for the completion of a task. This suggests that the combined effort of both camps will result in an optimal machine, but closer examination reveals that things are not so simple. For instance, perhaps it is the case that for larger systems, performance saturates with increasing device speed, and devices beyond a certain speed offer no further increase in performance.

The controversy over the relative virtues of global and local computation cannot be resolved unless optimization over several levels of abstraction are performed (see [9] and references therein.) Globally connected systems allow fewer steps of computation but result in longer duration per step, whereas locally connected systems require a larger number of steps with shorter duration per step; these considerations being closely related to the choice of algorithm, architecture, and interconnection media. To find the optimum degree of globality or locality, one must optimize jointly over possible algorithms and physical realizations of the machine.

The difficulty of introducing optical technology despite its clear fundamental physical advantages can to some extent be explained in the light of the above discussion. If we had a theory of computing which allows joint optimization over all levels of asbtraction, we could throw in the possibility of optical interconnections and switching into the parameter space. Then, given a computing task, we would perform the optimization, which would not only clearly indicate whether and when we should use optics, but also the architectures and paradigms that must be used. Since we cannot do this, we instead try to show that, say, a globally connected interconnection network is faster if implemented optically. But what if a locally connected network, which can be implemented electrically, allows the same task to be done in overall less time by running a different algorithm? (We have argued that this is not the case in [9], but not definitively.)

# 2.2 Alternative systems of levels of abstraction for general purpose computing?

It is clear that a very fast, large, and low switching energy array of optical switches or "smart pixels" has tremendous computing potential. However, it is too difficult a task to start from this array and arrive at a general purpose system in a single leap. If we are interested in designing a general purpose computer, we must guide our efforts by some system of levels of abstraction. It is first necessary to show how certain elementary functional units (in the abstract sense) can be formed, and then how these can form higher level units and so on, until we arrive at some kind of high level "programming language" enabling the problem description to be formulated.<sup>4</sup>

We could try to come forward with a new system of levels of abstraction complete with the techniques necessary for realization of each level, and then build machines including optical components based on this system. Taking the array of optical switches as our starting point, and without being biased by the mainstream system of abstraction, we may try to work our way up to the level of problem description.

Some alternative systems of abstraction do already exist, such as cellular automata, connectionist systems, and most significantly parallel computing. There is some reason to think that these might house optical technology better, but unfortunately these "paradigms" (which differ from the mainstream in varying degrees) are not that well developed. For instance, the techniques for only the lowest levels of abstraction are developed for cellular automata; nobody has a high-level programming language which they can compile into some kind of "assembly language" which will run on some kind of cellular automata

<sup>&</sup>lt;sup>4</sup>It should be clear that the burden of providing a higher level platform, which must rest on intermediate level platforms, belongs to whoever provides the computer. People will certainly be reluctant if they are presented a multi-stage array of programmable optical logic devices, no matter how fast or large, if we cannot show them where to plug the keyboard and monitor, and where to buy a C Language compiler. Without any registers, accumulators, microprocessors, assembly or C Languages, no user will want to program or configure their systems at such a low level.

hardware (which consists of several levels of abstraction down to the level of a single cell). The state of development of techniques for doing things with cellular automata is comparable to that of low level logic in the mainstream system, such as shift registers etc., and are not even at the level of a data flow architecture, let alone a microprocessor.<sup>5</sup>

In conclusion, it seems difficult to come forward with a general purpose optically interconnected computer based on such novel paradigms; the development of the mainstream system of abstraction having spanned at least a century.

#### 2.3 General purpose systems versus special purpose systems

Unlike general purpose systems which can be programmed to do any task with reasonable efficiency, special purpose systems are "hardwired" and can do only certain prescribed tasks. The more general purpose a computer is—that is, the greater the range of tasks it can do with reasonable efficiency—the greater the number of levels of abstraction it has. The more special purpose a computer is, the fewer (for instance, the abacus does not have many). Thus, special purpose systems provide a better opportunity for new technologies (such as optics) and underdeveloped paradigms (such as cellular automata).

Midway between the extremes of special purpose and general purpose systems we can identify a class of systems which we may refer to as "quasi-general purpose" systems or "coprocessors." Such systems can perform a certain class of operations of general utility, such as math coprocessors or digital signal processing chips. Of course, the full picture is that there is a continuum of systems of varying degree of "general purposeness" between the two extremes of special purpose and general purpose systems.

The "programming" of a general purpose system can take place at various levels. A microprocessor is a custom designed chip which can be programmed at a fairly high level (assembly language). On the other hand, a system to do the same task can be programmed at the much lower hardware level, for instance, by customizing a gate array. Both the microprocessor and the gate array can be viewed as general purpose systems which can be programmed to perform special purposes; the difference is in the nature of the programming and the level at which it takes place.

Under the light of what has been discussed until now, it is no wonder most successful optical systems to date have been special purpose systems. Such systems can be designed to perform a certain task standing alone, or they might be designed as a self-complete component of a larger computing machine. There is nothing complicated with the former. As a very simple example, an array of optical devices might be used as an image amplifier in a medical imaging system. The intricacies involved in the latter case will be discussed later.

<sup>&</sup>lt;sup>5</sup>It has been shown how to simulate conventional logic operations in cellular automata, so that one can in principle do anything with a cellular automaton that one can do with conventional logic. However, this is a meaningless approach if the cellular automata is implemented using logic gates in the first place, or simulated on a workstation. But things may change if cellular automata are implemented by virtue of some atomic scale physical phenomena etc.

<sup>&</sup>lt;sup>6</sup>It does not take much to be able to do any task, if one allows for gross inefficiency.

<sup>&</sup>lt;sup>7</sup>It is quite conceivable for a limited number of, say, image processing researchers to start from a description of the capabilities of an array of optical devices and devise algorithms and methods for performing tasks they are interested in. (Many researchers were interested when the systolic computation paradigm was introduced for VLSI systems, unveiling a new class of solvable but unsolved problems.) The key issue seems to be that it should be possible for a single group or working unit to be able to obtain fruitful results by themselves, since this will give them the incentive to attack the problem. On the other hand, the effort towards the general purpose system would require a much bigger effort, requiring strategic commitment by a larger institution.

Researchers and engineers make carreers out of solving the problems associated with a certain level of abstraction in the mainstream system. They will not be willing to change their focus easily, since within the present system, the people working at the lower level are providing them with the technology to realize their stuff, and the people at the higher level want the stuff to realize whatever they are doing at their own level. No one will benefit from change unless everybody changes at once. This is a particularly severe kind of "chicken-and-egg problem," since it is not regenerative (that is, it will not by itself change for the better once given a sufficient but small initial momentum). On the other hand, there are always people willing to work on special purpose systems, which due to their limited number of levels of abstraction can be handled self-completely by a single person or group. Thus, successful exposition of the capabilities of optical technologies to the image processing and computer science communities may be rewarding.

An issue which perturbs these considerations is the fact that in areas of academia where theoretical achievements are valued, the interest of researchers may be independent of whether they can interface with upper or lower levels of abstraction.

#### 2.4 Introducing optics into general purpose systems

Although we have seen that special purpose systems provide a conceptually simpler opportunity for optical technologies, we wish to explore how optics may be introduced into general purpose computing systems as well. Since we have seen that it is very difficult to come forward with an all-together novel system of levels of abstraction which would house optical technology in an efficient way, it is clear that general purpose computers will be mostly based on the mainstream system of levels of abstraction (which we might be able to modify to a limited degree).

First, let us consider modifying only the least abstract level of problem solving, the level of physical devices, wires, etc. In this approach, we start with the mainstream architectural and packaging paradigm and see whether it is possible to make a "better" machine by using optical components (interconnections and/or switches) instead of some of the electrical ones. Examples of this approach might be the introduction of optical backplanes or chip-to-chip modules instead of their electrical counterparts, while leaving the architectural conception and logical structure of the machine intact. This would change the job of the device physicist<sup>8</sup> and the person who designs the physical packaging, but would not affect people working at higher levels of abstraction, including those contemplating the logical and systemic architecture of the machine, as well as those providing the software.

This approach is appealing in that we do not have to worry about the development of new architectural concepts. However, there is no reason why the existing concepts should be particularly congenial to optical technology. In fact, they have historically developed to benefit from the strengths and accomodate the weaknesses of electrical technology, which are in some senses complementary to those of optics, so that this approach may not bring out the best of optical components. (VLSI architectures which try to minimize the length and number of chip to chip interconnections provide a good example.) Nevertheless, this may still be a valid and promising approach because it seems that replacing the longer wires with optical links does indeed result in a net advantage, even in existing systems.

If instead of the above simple approach, we wish to modify higher and higher levels of abstraction with the hope of better utilizing the particular optical technology at hand, we must face and overcome certain difficulties. For instance, we may attempt to replace a complete electronic combinatorial or sequential logic unit with an optical one which provides the same functionality, but in a "better" way. The interior structure and levels of abstraction of the optical unit may be entirely different, but it must interface with the system of levels of abstraction of the machine in which it is embedded at a certain level.

At relatively high levels of abstraction we might contemplate an optical microprocessor or digital signal processing coprocessor. At yet higher levels the physical and logical architecture of the machine will be altered significantly to suit the strength of the optical technology. For instance, we might contemplate an optically interconnected parallel random access machine where the processor locations and algorithms are designed so as to match precisely the type of connection patterns that can be provided by optics.

Modifying the system at higher and higher levels of abstraction so as to better suit the optical technology becomes an increasingly difficult task as we move upwards because of the need to maintain continuity between the different levels. If the central processing unit of a machine works on 32 bit wide words, its replacement must also work with 32 bit words. (It must be "plug compatible.") As another example, if we are to replace the existing electronic memory with an optical one, the input-output characteristics of the new memory must match those of what is being replaced. Notice that this requirement may sometimes resist improvements. A new optical memory, which provides much faster parallel access, may offer no system improvement, since the system in which it is embedded may not be able to utilize it. This makes it difficult to justify the optical technology, since the potential increase in performance offered by the optics cannot be utilized in this case, while its usually greater price will have to be paid.<sup>9</sup>

If we cannot succeed in getting a successful interface at one level, we might have to move up to a

<sup>&</sup>lt;sup>8</sup>More precisely, it would create jobs for some device physicists while eliminating jobs for the others.

<sup>&</sup>lt;sup>9</sup>On the other hand, perhaps an optical processor can be used to perform, say, some kind of parallel search on the data read from the optical memory, a feat which would be very expensive or slow with an electronic memory. The question now is whether the next higher level of the system can beneficially use the results of this fast parallel search. The answer would probably be ves if the search ouery as well as the result consist of small amounts of data.

higher level and try our chance at that level. By modifying this higher level (which may or may not involve optical components), we might be able to exploit the higher parallelism or bandwidth offered by optics. If not, we might have to move another level up, until the the intrinsic advantages of the optical technology seep through to the surface and translate directly into a user level performance advantage (such as getting the job done in less time).

This discussion should also clarify what is meant by doing something "better." Doing some intermediate level operation cheaper, faster, larger, etc. by introducing certain modifications at that level do not automatically result in user level improvements. It may be necessary to make further modifications at higher levels, until the fastness, cheapness, etc. can seep through to the user level (which is the highest level).

Modifying the system at a certain level of abstraction might correspond to introducing an optical subsystem (such as an optical logic unit) into the machine. but this need not be so. Remember that replacing all of the electronic switches and wires with optical ones does not alter the system of levels of abstraction at all, although we now have a computer consisting entirely of optical components. Alternatively, we may modify the architecture of the machine drastically, without introducing any optics at all. Despite the fact that the interconnection and packaging hierarchy often mirrors the levels of abstraction, the two concepts are distinct and must not be confused.

Before drawing some conclusions, we discuss a few examples to make the content of the last few paragraphs more concrete.

High-bandwidth "transparent" photonic switching Research in guided-wave wideband switching networks has resulted in rather impressive switches whose various strengths and weaknesses are not exactly matched to the requirements of existing multiplexed switching networks, so that it seems they may find less application than originally hoped for. The weakness of these switches is that they have a limited number of spatial channels. Their strength is that they can route very high-bandwidth signals transparently. Efficient use of this bandwidth cannot be made if bitwise multiplexing is employed, since these systems cannot switch at a rate as high as their transmission bandwidth. However, if we make the higher level modification of employing large-size block multiplexing instead of bitwise multiplexing, we can walk around this disadvantage. Now we must face the issue of whether the use of large-size block multiplexing is compatible with the next higher level of abstraction (which might be that of communication protocols and transmission standards). If not, we may try to push forward by suggesting modifications to the protocols and standards. If we do not arrive at a clear advantage within a few levels, we might have to give up.

Two-dimensional digital optical image processing Optical technology will probably make it possible to construct image processing subsystems which can perform two-dimensional signal processing operations (such as the discrete Fourier transform (DFT), convolutions, etc.) in parallel at a very fast rate. Given the fact that digital electronic hardware is extremely strained to perform such operations of even moderate complexity, it initially seems that digital optical signal processing coprocessors would have much to offer. However, it is not immediately clear how such an optical coprocessor can be interfaced to the rest of the system. Setting up the two-dimensional data serially from conventional electronic memory may largely nullify the potential advantages of such a system. <sup>10</sup> The limitation is actually that of the electronic processing system as a whole, which cannot handle larger amounts of data in parallel, not of the optical coprocessor. But the bottom line is that it may not be possible to improve overall performance by simply replacing the coprocessor, because the rest of the system is not good enough to take advantage of the increased capacity and speed. (One should not exclude the possibility that in some cases the replacement might indeed prove beneficial, despite the bottleneck involved in serial transfer at the interface, or there may be no interface problem because the data is already in optical form (coming from an optical memory or natural image). Nevertheless, it is likely that in most cases the capabilities of the optical subsystem will be largely underutilized due to this interface problem.)

<sup>&</sup>lt;sup>10</sup>This has been referred to as the "fire hose problem."

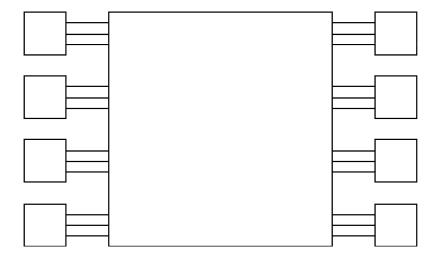

Figure 1: The large block in the middle represents global operations on the whole image. The smaller blocks on the left and right represent local operations on parts of the image.

Does this mean there is no possibility of employing optical technology short of contemplating an all optical system from scratch, which we argued was a very difficult task? Not necessarily. Some modification in the higher level design of the system may enable a successful interface. The strength of optics in this case is that it can provide the interconnections necessary for the global flow of information, which electronics cannot. The strength of digital electronics is that it can provide complicated operations in a small space, which optics cannot. Thus, successful partitioning (or "factorization") of the overall problem to match the strengths of both technologies may lead to an architecture of the kind depicted in figure 1. The big block may represent an operation requiring regular global interconnections (implemented optically), whereas the smaller blocks represent digital electronic processing. The many smaller blocks on the left work on parts of the data independently in parallel and feed the optical subsystem in parallel, so that there is no serial bottleneck. After performing the necessary operations, the optical subsystem distributes the large array of data to the several digital processors on the right for subsequent processing.

In conclusion, we see that beneficial use of an optical subsystem may require integral redesign of the system architecture at one or more levels above that at which the optical subsystem was introduced.

**Parallel memory access** Recent developments promise high speed parallel random access of huge amounts of data from silicon as well as optical memories. The former involves optical devices integrated with silicon, whereas the latter involves transmissive or reflective readout from optical storage media.

The considerations here are similar to those in the preceding example. Although the large archival storage capacity of optical memory can be utilized without difficulty, its potential for fast parallel readout may not, unless system architectures are designed in a way that make this possible. Once again it seems that parallel architectures in the spirit of that suggested in the previous example might be useful. Alternatively, some form of optical processing may be used to distill the large amounts of data read from the optical memory, returning a small amount of information that can be handled by the electronics at the higher level. This might be useful in database applications.

Photonic digital (logical) switching Digital photonic switches are essentially optical/optoelectronic logic circuits, often based on multi-stage switching network architectures, which enable a given pattern of connections to be established between a large number of incoming and outgoing communications lines [20].

Since the large number of incoming and outgoing lines coming from distinct locations are simply bundled together to form the "fire hose," the interface problem discussed in the image processing example

does not arise in this case. This makes optical technology particularly suited to this application.

#### 2.5 Some conclusions

In conclusion, optical technology can be beneficially introduced into a general purpose computer if we can come up with modifications to a system involving the use of optical components in such a way that the intrinsic advantages of the optical technology result in user level improvements.

A particularly transparent special case is to replace an electronic subsystem with an optical one of identical functionality, such that the user level figure of merit is improved by the change in subsystem operating parameters (cost, speed, number of channels, etc.). The internal structure of the optical subsystem may be completely different from the electronic one.

The simplest special case of the above is to replace certain electrical switches or wires by optical ones without otherwise modifying the system. Examples are optical backplanes, fixed free-space interconnections between circuit boards, etc. (In this case, no change is made to the existing system of levels of abstraction. A backplane or free-space interconnection system is not a subsystem in the sense of the previous paragraph.) This may not be the best way to utilize optics though, so that dissapointments in this approach should not be used to judge the potential of optics.

However, it is very difficult to do something useful with an optical technology (despite its large speed and parallelism), if it cannot be interfaced to a certain level of abstraction of an established architecture in a seemless manner. Otherwise the user level problem description is too many levels away to make optical device arrays or the like useful for general purpose applications.

On the other hand, special purpose applications where the product can be provided in a form which can be directly used without requiring any low level "software" development by the user or third parties are clearly promising. Examples might be integrated optical detection planes for image preprocessing, dedicated image processing functions, "smart" optical sensors, etc.

We will not aim at providing a comprehensive elaboration of the general philosophy outlined above, but will rather concentrate on a certain optoelectronic hybrid integration technology, that of flip-chip bonding of SEED's on silicon. Of course, similar considerations apply for other technologies exhibiting similar characteristics.

## 3 Optoelectronic integration technology

In this section we outline the essentials of a particular technology (or set of technologies) which we believe will serve as a useful platform to discuss the opportunities for optics as well as to implement them in the short term. We also discuss certain architectural and system level issues and alternatives.

#### 3.1 Hybrid integration of SEED devices with silicon

Initially, self-electrooptic effect devices (SEED's) were constructed as bistable circuits which could be used as latches and logic gates. This was true of the older two-terminal devices as well as the newer three-terminal devices, including the symmetric SEED arrays (S-SEED's). Later, FET-SEED technology [12] was developed as the interest in cointegration of transistors and optical devices increased. This interest was driven by the needs both to reduce optical input power (through transistor gain) and increase logical complexity (through transistor logic). A certain degree of non-trivial functionality, such as Boolean logic, is also possible between the pixels of S-SEED arrays, but not comparable to what can be done with transistors [13]. The monolithic FET-SEED technology may ultimately provide high-performance and low cost optoelectronic circuits. In the short term however, it seems wise to capitalize on the very advanced state of silicon technology by hybrid flip-chip bonding of SEED's on conventional silicon chips<sup>11</sup> [11]. This offers great flexibility in that we can design any kind of electronic circuits around the optical

<sup>&</sup>lt;sup>11</sup>The relative importance of the monolithic and hybrid technologies depends on the extent that systems want very high logical complexity (e.g. number of transistors) or very high device performance (e.g. clock frequency).

devices. The technological possibility of being able to combine substantial amounts of optical inputs and outputs, with respectable performance, with essentially any complexity of silicon raises entirely new system possibilities. Indeed, it is one of the purposes of this paper to explore what these new systems might be.

The optical devices (the detectors and modulators) will probably will laid out on a regular array for simplicity and solder bonded to regularly spaced pads provided on the silicon. There are a number of different ways of looking at such a system. First, we can look at it as a conventional silicon circuit with optical input and output ports provided on a regular array. While shorter connections are established electrically in the usual way, longer connections may be provided via the nearest optical modulator and detectors.

An alternative view is that of looking at the system as an array of "smart pixels", each of which exhibit considerable functionality made possible by the electronics below. The electronics associated with each pixel may constitute isolated electrical islands, but we may also have pixel to pixel connectivity in the silicon if desired. If we consider the defining quality of smart pixels as their regular periodic structure, then we may consider them as "gate arrays" of silicon circuits with optical ports. The term smart pixel is artificial and exists for historical reasons, deriving from the evolution of the idea from optical logic arrays ("dumb pixels"). What is a smart pixel array and what is just an optically interconnected chip is perhaps best decided by the application. (It is also interesting to contrast these systems with spatially continuous (unpixellated) spatial light modulators such as those based on liquid crystals etc.)

Currently it seems that an optical input-output can be placed within every  $50 \,\mu\text{m} \times 50 \,\mu\text{m}$  square, set by requirements of the soldering pads, with the size of the optical devices themselves being about  $10 \,\mu\text{m}$ . A possible 2cm chip might then contain  $400 \times 400$  "pixels." The density of pixels attained seems close to that predicted as optimal by several system level studies [7, 10]. These figures also seem to be consistent with the number, separation, and spot size of the optical beams that can be generated and manipulated with the required quality.

Yield considerations limit the size of the chip and thus the total number of pixels. Currently about a thousand to ten thousand pixels seems possible.<sup>12</sup> These devices can be expected to switch in less than a nanosecond, and the energy per optical event can probably be made small enough (less than a picojoule) that it can be ignored in comparison to the energy dissipated in the silicon. If operated at the contemplated fast rates, it will be necessary to mount these chips flat on a heat sink [14].

One interesting prospect for this (or FET-SEED) technology is that of patterning holographic optical elements directly on top of the optical devices, by introducing a few additional steps to the planar process [15]. A few layers would be needed to emulate a thick hologram with single diffraction order. One can imagine these integral optical elements being used in conjunction with a single mirror above the plane of the devices.

A number of issues such as single rail versus dual rail encoding, transmissive versus reflective devices, light sources versus modulators, and associated beam combination are discussed in [20]. It seems that there are benefits to working with dual rail encoding, reflective devices, and modulators as opposed to their alternatives. Dual rail encoding allows insensitivity to parameters that may drift across the system, reflective devices are apparently easier to fabricate and allow for heat removal to take place from the other side, and modulators are preffered for a number of device based reasons.

We will refer to a silicon chip furnished with optical inputs and outputs as an optoelectronic device plane.

<sup>&</sup>lt;sup>12</sup>One or two orders of magnitude more would be desired for image processing applications. However, the high speed of the devices compared with video rates might allow partitioning the image much as in the case of conventional electronic processing, or perhaps multiplexing sets of pixels together. (It is also interesting to speculate as to whether optics might somehow allow us to operate with technologies in which not every device has to work. If it could, we could break free of the size and scale limitations that absolute perfection impose. One might, for example, customize the optical interconnection pattern so as to bypass the defective units (or perhaps even customize at some higher software level). Such an idea is conceivable with arrays of identical, isolated smart pixels since parallel optical testing of the finite isolated pixels would be possible. Such approaches could allow very large systems not limited by yield or testing.)

#### 3.2 Free-space optical interconnections

The various issues pertaining to free-space optical interconnections have been discussed in detail in [16, 17, 18, 19, 20], and will be only briefly touched upon here.

Space-variant or nearly space-variant connection patterns, or connections patterns exhibiting a certain degree of regularity or symmetry such as the Banyan, crossover, and perfect shuffle can be implemented with relative ease and high space-bandwidth product utilization efficiency. Other space-variant and irregular patterns of connections can be implemented directly with multifacet approaches, but in a space-bandwidth inefficient way. Arbitrary connection patterns can be obtained in a efficient way by employing a  $\sim \log N$  stage architecture, but at additional complexity. Most desirable is to contemplate the higher level architecture of the system such that it relies on only a regular or space-invariant pattern of global connections. Many excellent examples of such architectures exist [20].

The manipulation of optical beams among the device planes introduces stringent requirements on the quality of the optics. Obtaining uniform distortion free spot arrays with a single lens over large extents is difficult;  $64 \times 64$  arrays have been successfully utilized in systems [21], but it seems that larger arrays of even  $100 \times 100$  pose a considerable challenge.

#### 3.3 Heat removal considerations

Heat removal is one of the most significant issues for large three-dimensional systems. Various considerations suggest arraying all device arrays on a single heat sinking plane and providing optical interconnections on the other side of the plane [14, 23].

#### 3.4 Physical architectures for optoelectronic systems

We now discuss architectural issues at a slightly higher level. We use the term "physical architectures" to distinguish our discussion from a discussion of logical architectures, which is at a yet higher level. The two concepts are nevertheless not unrelated; for instance, a multistage switching architecture maps naturally onto a multistage cascade of device planes.

It is simpler to imagine we are working with transmissive single rail systems with light sources, but we maintain the understanding that these can be converted into dual rail reflective systems with modulators without much difficulty.

Processing systems can in principle be designed by employing a continuum approach. In this approach we tailor the refractive index, nonlinear properties etc. of an optical medium such that it performs the desired operations on an optical signal. Since the design of such systems would be difficult, most practical design methodologies favor discrete thinking: wires and beams instead of waves, switches instead of continuous nonlinear media. In order to have a designable, manufacturable system, we discretize (and perhaps quantize) all optical signals, and segregate the nonlinear operations (realized as point operations) from the linear operations (realized through propagation and filtering). Despite such discretization, with a little imagination we can view the signals as "propagating" in some discrete space with certain rules of its own.

Computer architectures based on the optoelectronic device plane and free-space optical interconnection technologies described in previous subsections, can be classified based on several properties:

1. Whether they consist of a single device plane or many.

A single device plane may receive its inputs in optical form and delivers its outputs in optical form, serving as some kind of optically controlled spatial light modulator. The inputs and/or outputs may be intrinsically optical (e.g. optical memory, natural image), or interfaced with other system units with optical inputs/outputs. Alternatively, the input or output may be read in or out electronically, in which case the device plane also serves as a transducer. In any event, all but minor processing is done electronically. Depending on the application, the optics preceding and following the device plane may be relatively sophisticated, perhaps performing various linear global operations.

Systems containing multiple device planes with free-space optical interconnections between them offer various architectural options, which are discussed next.

- 2. Optically interconnected array of device planes versus multistage cascade of device planes.

- i.) It is possible to simply array a number of device planes in some two or three dimensional geometry and provide optical interconnections among them. This presumes that some form of circuit is going to be partitioned between the device planes and that the chip to chip connections are going to be made optically.

- ii.) On the other hand, it is possible to cascade device planes in a sequence such that each has connections only with the immediately preceding and following planes. The pattern of optical interconnections between consecutive stages would most likely be regular patterns, since these are more efficiently implemented.

This classification is somewhat skewed, since the first option is much more general, and includes the second as a very special case. Many other special cases corresponding to, say, systolic, cellular, or other paradigms could also be singled out. Other special groupings or connection topologies for the several device arrays can also be considered.

The privileged status of the multistage architecture can be at least partly attributed to historical reasons. Conventional optical systems (e.g. telescopes) have the general form of planar or quasi-planar optical elements cascaded along an optical axis. This general form can be seen in analog processing systems, and also in generic digital optical computing schemes in which one or more device planes are connected in cascade with various optical elements, all aligned along an axis, with the output of the system tied back to its input in a form resembling a finite state machine.

It may be beneficial to break this bias and explore other possibilities. The simple linear sequential arrangement is the simplest connection topology possible; a vast number of alternatives remain to be explored. Notice that here we are not talking about the connection topology between the pixels of two planes (which we presume will be one of the regular patterns discussed previously), but of the connection topology between the device planes. There seems much to investigate in terms of which topologies may be useful and at the same time allow a clever optical arrangement of the many bundles of connections among the many device planes. One approach would be to implement a processor on each device plane, and connect these processors to each other according to some multiprocessor interconnection network. The large number of space-invariant/regular channels among the connected processors will allow fast transfer of large amounts of data from processor to processor.

It is worth noting that in any case, the use of reflective devices and heat removal considerations will most probably force all device planes to be arrayed on a single surface, even if logically we tend to imagine the multistage architecture in the form of a sequential stack of parallel planes. (This is actually true of the most sophisticated optical digital systems yet built [21, 22].)

3. Unidirectional or bidirectional information transfer.

Multistage architectures are usually contemplated as a feedforward pipeline in which information flows always in the same direction through the sequence of planes. Alternatively, it is possible to allow connections in both directions, allowing greater flexibility in design.

In both cases, it is possible to connect the last plane in the sequence to the first, so that the information can loop or iterate through the system (in the first case) or we have a cyclic system (in the second case). (A simple example of this is an optical "bus" connecting boards on a backplane.)

It is important to be aware of fully electrical quasi three-dimensional integration technologies. Multichip modules with the order of fifty interconnection layers allow a considerable amount of wiring space. More impressive is solder-bump bonding of the order of tens of active electronic chips [24]. The density of the chip to chip "vias" (spaced  $\sim 0.2 \,\mathrm{mm}$  apart) is comparable to that of the density of optical "pads" possible with the optical technology outlined above. Thus the number of out-of-plane "pinouts" offered

by both technologies are similar. However, only local (right across) interconnections are possible with the electrical technology, whereas global connections are possible with the free-space optical technology. Furthermore, these electrical connections may have large capacitance or inductance and thus limited speed, compared to the optical connections that should be able to operate at high speed and bandwidths.

The device plane concept may be generalized to allow for such multilayer structures, be they multilayer wiring substrates or multiple active planes as described above. Optical devices would be mounted on the outermost layers of such stacks. The resulting compound device planes would be able to provide more silicon circuitry per optical pixel, should that prove desirable.

#### 3.5 How much silicon per optical pixel?

One of the several general issues and problems that might be treated with respect to a particular application is the problem of adjusting the optical pixel density with respect to the electronic circuit density, assuming that we want to implement a particular pattern of connections, perhaps with a specified line length distribution.<sup>13</sup> In other words, how do we break a circuit into smart pixels? This problem is essentially the same as that treated in [5, 7, 10], so that one can arrive at specific conclusions for a particular situation by modifying the treatment in these references.

#### 3.6 Analog versus digital

We distinguish between discreteness in space, time, and amplitude. In conventional optical processing, continuous spatial light modulators allow manipulation of spatially continuous images. The technology under consideration inherently introduces spatial sampling, even if the objects we are working with are continuous signals or images. Circuit based computations (e.g. logic) are inherently spatially discrete anyway. Although perhaps not intrinsically necessary, the optical technology under consideration will most likely impose temporal discreteness as well (clocked operation with short pulses).

What remains for us to decide is whether to work with signals that are discrete or continuous in amplitude (i.e. digital or analog). Both approaches are compatible with the technology.

One of the major factors hindering the widespread use of optical processing despite its enormous temporal and spatial bandwidth has been its low amplitude accuracy. If the new technology is going to overcome this weakness, digital operation is probably to be preferred. The high speed of the devices will allow quantized optical amplitudes to be bit serialized, without sacrificing any spatial parallelism.

#### 3.7 Prospects of the technology

It will be worth restating some of our previous conclusions for the technology under consideration. The options for utilizing this technology seem to be as follows:

- 1. To use it for special purpose applications, if these can be identified.

- 2. To use SEED on silicon technology simply as a way of wiring up circuits designed under the conventional paradigm (low level modification). This is a special case of the next item.

- 3. To identify a component or subsystem of a conventional electronic computer which constitutes a bottleneck, in the sense that replacing this component or subsystem with one that is faster (or cheaper or can handle larger amounts of data etc.), will result in the overall computer to be faster (or cheaper or able to handle larger amounts of data).<sup>14</sup>

<sup>&</sup>lt;sup>13</sup>The problem is colored by the fact that if we use a regular global pattern of optical interconnections, arbitrary irregular connections will have to involve local electrical "fine routing."

<sup>&</sup>lt;sup>14</sup>One might propose that every existing computer has a limiting component or subsystem, which is true. Nevertheless, situations in which replacement of a component or subsystem would result in substantial overall improvement may not be commonplace, since the historical evolution of design concepts and technology has a tendency to balance the various components and subsystems in a way that no component is "overqualified" for the purpose it serves.

If such a component or subsystem is found, it would be beneficial to replace it with an optical one which exhibits improvements in the relevant characteristics. For instance, if the clock rate or power dissipation of a computing system is determined by the longest wires, and we can reduce the delay or dissipation along these wires by replacing them with optical channels (as suggested in the previous item), we can obtain a net improvement at the level of the overall computer. As another example, assuming that the speed of a computing system is solely determined by the memory access delay or the time it takes a coprocessor to invert a matrix, replacing these subsystems with optical ones may result in direct benefit.

4. If the conditions for successful application of the previous item do not exist, either because the optical technology is not directly compatible with the higher levels, or because its intrinsic advantages are buried at that level, modify the system architecture a few levels upwards with the hope of achieving the goal of the previous item (e.g. as in the example on page 7).

We have seen that the strength of the electronics is its flexibility in providing arbitrary operations and its weakness its inability to provide global connections. The strength of optics is precisely the weakness of the electronics. Thus, the beneficial use of the outlined optical technology is mostly dependent on whether a particular application can be efficiently decomposed (or "factorized") into stages of globally connected operations.

## 4 General purpose systems

As we have discussed, replacement of electrical components by optical ones in a mainstream system architecture is a possible approach with a certain promise. The silicon chips with optical inputs and outputs can be physically arranged in many different ways. Several considerations suggest arraying the chips on a planar substrate which also serves as a heat sink [14]. Lenslet arrays or holograms immediately above the detectors and reflective modulators, together with an overhanging mirror or further holographic elements may provide the optical imaging. Less aggressively, the optical pinouts can be used to provide board to board connections between boards stacked on a conventional rack.

On the other hand, the development and utilization of new general purpose architectures is more difficult, despite the fact that various possibilities have been suggested or come to mind, such as pipeline processors based on cascades of optically interconnected arrays, parallel machines based on parallel random access machine (PRAM) models, etc. Optically interconnected parallel computers will be discussed further in section 10.1.

Apart from this, fully general purpose systems will not be further discussed here, although some of our discussions below might be relevant for such systems as well. We will first discuss special purpose systems, with emphasis on image processing. We will then discuss what we call "quasi-general purpose systems" (or "coprocessors" or "generic subsystems"), such as logic units, memory, matrix processors etc.

## 5 Special purpose systems: information processing

Special purpose systems by definition are hardwired to do specifically one or a few jobs. An image plane processor which differentiates the input image will be considered a special purpose system, whereas a processor which can multiply an image with any given matrix will be considered a quasi-general purpose system.

Special purpose systems can be classified as those which manipulate pure information, and those which interact with the physical environment. The former category is the subject of this section (in which we discuss special purpose systems by application area, with the major emphasis being on image processing), and the next section (in which we classify the necessary operations by their information flow requirements). The latter category is the subject of section 7. Quasi-general purpose systems will be discussed in section 8.

#### 5.1 Image processing

The use of conventional optical systems for processing images has been widely suggested and to some extent realized. Such systems have usually suffered from a lack of quality spatial light modulators and insufficient dynamic range. Both problems are alleviated with the digital technology under consideration.

Image processing applications are often classified as image enhancement, filtering, restoration, analysis, reconstruction, compression, etc. We first give a short overview of these, referring the reader to [26, 27, 28] for details. Afterwards, we move on to categorize the elementary operations used in these applications in terms of the optical architectures they might require, which is a more useful classification for our purpose.

The following list, which is strongly based on [27], should not be taken to be exhaustive but rather as representative of the mainstream of image processing techniques, development, and research. (Certain generalizations such as multispectral, color, or adaptive processing are not explicitly considered, but represent possible extensions.)

Image enhancement Operations used for image enhancement can be classified as:

- 1. *Point operations*: contrast stretching, clipping, thresholding, negation, level slicing, bit extraction, range compression, histogram modification.

- 2. Spatial operations: noise smoothing with linear or nonlinear (e.g. median) filtering, unsharp masking, low-pass, bandpass, high-pass filtering, zooming.

- 3. Transform domain operations: linear and nonlinear filtering in the transform domain.

#### Image filtering, restoration, estimation, and prediction The methods used in this area are:

- 1. *Linear filtering*: inverse filtering, Wiener filtering, interpolation, least squares and singular value decomposition methods, iterative methods, recursive (Kalman) filtering.

- 2. Statistical and information theoretic methods: Bayesian methods, maximum entropy methods.

- 3. Geometric methods: coordinate transformations and geometric mappings.

#### **Image analysis and computer vision** The procedures in this area can be grouped as follows:

- 1. Feature extraction: extraction of spatial features (amplitude and histogram), transform features, edges and boundaries, shape features, moments, texture.

- 2. Pattern recognition: matched filtering and detection.

- 3. Segmentation: template matching, thresholding, boundary detection, morphology, clustering, texture-matching.

- 4. Classification: clustering methods, statistical methods, decision trees, similarity methods.

**Image reconstruction from projections** This area involves operations such as the Radon transform and its inverse, back projection, as well as standard operations such as convolution, Fourier transforms, filtering, and (matrix) algebra.

Image data compression This currently very active field may be broken down as follows:

- 1. Pixel coding: temporal pixelwise pulse-code modulation, run-length coding.

- 2. Spatial predictive coding: delta modulation, differential pulse-code modulation

- 3. Transform coding: zonal coding, threshold coding.

- 4. Interframe (temporal) coding: adaptive spatial predictive coding, motion compensation.

**Image detection and display** Image detectors and displays constitute the interface of image processing systems with the real world. Useful processing may take place during detection or prior to display.

There has been some interest in developing smart image sensors inspired by biological examples. Animal eyes as those of humans have some local preprocessing, serving the purposes of mean luminance adaptation, contrast enhancement around edges etc. [29].

Smart sensor arrays that look at an image and draw some reduced data conclusions, such as for purposes of alignment, inspection, vibration monitoring, movement detection, autofocus, ranging, limited robot vision, or other simple task can be envisioned. As will be discussed in a later section, it is not clear that such local operations require the global connectivity of optics, but since the input is in optical form anyway, SEED on silicon technology may prove to be useful.

A simple, yet interesting example is the use of a smart pixel array to find a linear or nonlinear combination of a number of images, or the "distance" between two images in some vector space. Yet another might be, say, a medical viewing application where we enhance the image by using a smart pixel array. This would essentially be an electronic processor, but with optical input and output.

This application category may include optical memory readout and write systems as well.

**Generalizations** The above methods and operations can be generalized or refined in a number of ways, such as joint processing of multiple channels and color images, iterative, recursive, and adaptive processing, etc. Such extensions are not explicitly discussed but should be possible in most cases thanks to the flexibility afforded by the silicon.

For instance, iterative processing can be implemented by allowing several loops through the optical system, whereas adaptive processing would be possible by allowing each smart pixel to operate with different parameters which are updated as required by the algorithm.

#### 5.2 Communications switching

One of the simplest switching problems is that in which we realize a one-to-one mapping (a permutation) of N lines onto another set of N lines in the desired manner. More generally one can desire the ability to provide connections that are not one-to-one. The optical technology emphasized here is more suited to logical switching, rather than transparent relational switching.<sup>15</sup> In most cases the desired functionality can be achieved by employing a multistage interconnection network. Details can be found in [20].

#### 5.3 Sorting

Sorting N items with respect to a certain key is similar in nature to the permutation problem, and is also discussed in [20]. The sorting problem is important in that it is a basic operation frequently used by other algorithms.

## 6 Classification by information flow requirements

Image processing tasks are accomplished by performing various operations on the images. Above, the various operations were classified by application. Here, they are classified by optical architecture. We will identify several prototype operations and associated architectures which constitute equivalence classes in the sense that the difficulty and success associated with all members of a class are, or are expected to be, similar

While considering these operations, we directly associate the array of optical devices with pixels of the image, although a certain amount of multiplexing or spatial division might be required if the sizes of these do not match. (Other alternatives include piping in space-time chunks of the image sideways; that is, aligning the temporal dimension of the image with one of the spatial dimensions of the hardware.)

<sup>&</sup>lt;sup>15</sup>In such switches light is passively or actively routed but does not take part in any nonlinear interaction or switching itself.

We are also assuming that the number of optical pixels is of the same order of, or differs at most by a constant factor from, the number of pixels in the array to be processed. Thus, we exclude approaches where the number of optical pixels required are proportional to, for instance, the square of the number of pixels to be processed. This excludes multi-facet approaches [4] [19] to providing free-space optical interconnections.

It is also worth noting that in some cases the input image is transformed into an output image, but in other cases a certain amount of data reduction may take place so that some kind of feature vector, rather than an image, is produced as the output.

#### 6.1 Type I: point operations

Point operations are those in which the value of an output pixel depends only on the value of the corresponding input pixel.

These were encountered in image enhancement and coding (individual pixel coding) and might also include algebraic and logical operations on a small number of images, such as image addition and subtraction<sup>16</sup>, logical AND etc., and also amplitude feature extraction, temporal coding of arrays of data with no interpixel coding, and image detection and display.

Prototype operation: Nonlinear point operation on an image.

*Prototype architecture*: Single device plane with optical input and output. The silicon circuitry associated with each pixel is isolated from the others and performs the nonlinear operation, which may be space-varying, time-varying, adaptive, etc.

If several operations of this kind are to be performed consecutively, they might either be performed in place, or by pipelining the array of information through several consecutive device planes which are connected optically. In the latter case, the optics would simply image each pixel on any given plane onto the corresponding pixel on the next plane, creating an isolated pipeline for each pixel. Since the isolated pipeline for each pixel can be bunched or curled up within a single pixel, we conclude that optical interconnections are superfluous in this case. Even if we run out of silicon to do this on a single device plane, multi-active-layer electronic technologies can be used to construct the pipeline without any optics, since no cross connections are involved and the electrical interconnections would be short.

In evaluating the usefulness of optical technology in performing this type of operation, one should distinguish between two cases. That in which the data is available and/or required in electronic form and must be serially transferred to/from a two dimensional array, and that in which the data is available and/or required in two-dimensional optical form. In the first case, there does not seem to be a point in using any optics, as the task can be performed with an electronic array just as well. However, if the input and output of the system is to be in the form of a two-dimensional array of optical signals, then it might be useful to employ a smart pixel technology.

Thus, the question is whether and when the input and output would be in the form of a two-dimensional array of optical signals. If the rest of the system is a collection of units performing similar points operations, then the input and output will most likely not be such an array of optical signals, since the system would most likely be implemented electronically based on a similar argument as made above. However, if the rest of the system is performing global operations for which we will see optics is useful, then the data coming from and going to these stages will be in optical form, so that a smart pixel technology would be compatible with the rest of the system. Alternatively, the source of information may be intrinsically optical, such as in the case of a natural image or optical memory readout.

## 6.2 Type II: local operations

Local operations are those in which the value of an output pixel depends only on the value of the input pixels that lie within a reasonably small neighborhood of the original pixel.

Among these are most spatial operations used in image enhancement, most (but not all) of which can be expressed in the form of convolution or space-variant linear superposition with a relatively small

<sup>&</sup>lt;sup>16</sup>Operations on two or more images might be performed by introducign them consecutively, or by interlacing them.

window function (smoothing, median filtering, low-pass, high-pass, band-pass filtering, differentiating, interpolation). Finite impulse response Wiener filters extending over small windows and recursive (Kalman) filtering are some of the filtering and restoration operations falling into this class, as well as various image analysis methods such as histogram feature extraction, edge detection, boundary extraction, thresholding, most morphological operations, and texture feature extraction. We can also mention matched filter detection of small objects, spatial predictive coding, pyramid image coding (by coding the difference in consecutively low pass filtered versions), and image detection and display as operations requiring local operations.

Prototype operation: Nonlinear function over small window.

*Prototype architecture*: Single device plane with optical input and output. The silicon circuitry associated with each pixel is connected to those within a small neighborhood and performs the specified nonlinear operation.<sup>17</sup>

Our arguments for point operations are applicable to this class of operations as well. More silicon is needed to perform the more complicated operations, as well as to provide the interconnections which will carry information from/to nearby pixels. Nevertheless, provided the neigborhood (window) size remains small, the basic argument remains valid.

As we consider operations which require information from greater and greater neighborhoods, this category merges into the next (global operations). Eventually, after a certain point it becomes useful to employ optical interconnections. We do not treat this case of intermediate connectivity separately, but subsume it in the following subsection.

Even in the case of natural light input, such as a smart image sensor, it is not clear that the SEED on silicon technology has anything special to offer. Since the processing can be done electronically, the only use of optics is for detection. Thus we must ask ourselves whether a SEED detector array is better than, say, a CCD array. Perhaps a CCD array smartened with some silicon circuitry might be preferable to the technology considered here.

#### 6.3 Type III: global operations

Global operations are those in which the value of an output pixel may depend on the values of the input pixels across the whole image. We will classify such operations into three subtypes. For type A systems, we require it to be possible to decompose the operation such that it can be realized in a regular multistage system with a small constant number of stages. For type B, it should be possible to decompose the operation such that it can be realized in a regular multistage system with the order of  $\log N$  stages. Type C operations are defined as those in which the values of the output pixels may depend on the values of the input pixels across the whole image, and realization with a regular multi-stage system requires more than the order of  $\log N$  stages. The extreme case would involve  $N^2$  independent parameters to specify the relation between the input and output pixels, as in a matrix-vector multiplier or crossbar. (If there are only N degrees of freedom per stage, this would imply at least N stages.)