# Parallelization of C<sup>3</sup>M

#### M. Ozan KARSAVURAN

CS 533 – Spring 2015

### **Problem Description**

- Cover-Coefficient-based Clustering Methodology[1]

- Effective

- •Efficient?

### Motivation

- Moore's Law [2]

- Smaller but many core

- Need parallelism

#### Motivation

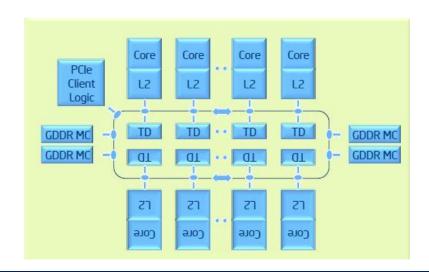

- Intel Xeon Phi [3]

- •Many Integrated Core (MIC) Architecture

- •60 Cores @ 1.053 GHz with 512 KB L2 cache

- Ring interconnect

- •4 hardware threads per core

- •1 Teraflop/s performance

3-April-15 Parallelization of C<sup>3</sup>M 4/8

### Methodology

- Implement of C<sup>3</sup>M

- Determine parallelizable sections

- Native vs Offload

- Small cores

- I/O

- OpenMP[4]

- Pragamas and Directives

## **Expected Results**

Speed up

3-April-15 Parallelization of C<sup>3</sup>M 6/8

### **Questions and Answers**

#### References

- [1] F. Can and E. A. Ozkarahan. Concepts and effectiveness of the cover-coecient-based clustering methodology for text databases. ACM Transactions on Database Systems (TODS), 15(4):483-517, 1990.

- [2] Schaller, Robert R. "Moore's law: past, present and future." *Spectrum, IEEE*34.6 (1997): 52-59.

- [3] Intel Xeon Phi Coprocessor the Architecture. https://software.intel.com/en-us/articles/intel-xeon-phi-coprocessor-codename-knights-corner. Accessed: 2015-03-20.

- [4] L. Dagum and R. Menon. Openmp: an industry standard api for shared-memory programming. Computational Science & Engineering, IEEE, 5(1):46{55, 1998.